#### UNIVERSITY OF COPENHAGEN FACULTY OF SCIENCE

**MSc** Thesis

# Quantum point contacts with complex gate geometry in high-mobility GaAs

**Emily Hajigeorgiou**

Supervisor: Anasua Chatterjee

Submitted: May 22, 2023

## Acknowledgements

This past year at QDev has been very productive for me, both scientifically and personally, and I highly value my time here. There are many unique aspects about QDev, but the people are definitely the soul of this place.

Anasua, thank you for keeping me focused and for encouraging me to push through, the grass is indeed greener on the other side. More importantly thank you for your constant support, regarding thesis work, and much more. Ferdinand, your enthusiasm about mesoscopic physics really resonated with me during CME, and made me want to join QDev, so thank you for that, and for discussions throughout the thesis.

Charlie and Sole, thank you for welcoming me in the Quantum Matter group, and special thanks to Charlie, it was a privilege to receive constructive feedback from you during the past year.

Fabrication has been a big part of this thesis. I am grateful to Smitha, thank you for your patience and careful considerations of the various problems I had. Thank you Sangeeth for your detailed recipes and help throughout my fab runs. I would also like to thank all the cleanroom staff for taking up the not-so-easy task of running the cleanroom, Martin, Nader, Zhe, Marianne. Finally I would like to thank the cleanroom ghost, for their Silent contribution and ideas! On this topic I should not forget to thank ALD1 for decorating my chips, but still allowing them to work.

My work was split between two groups. I firstly want to thank everyone in the Spin-Qubit group, thank you Fabrizio, Lazar, Harry, Tørbjorn, Fabio, Serwan, Will. Thank you all for helping out in numerous ways through the past year. Bertram, thanks for being my fab teacher's teacher. Special thanks go to my teacher, Tsung-Lin. You put up with my constant and annoying questions, and you essentially taught me how to be an experimentalist.

I would also like to thank the members of the Quantum Matter group, Magnus, Luca, Alisa, thanks for always being available for discussions and troubleshooting. Vasili, thanks for being the best fab student, and for our enlightening conversations. I would very much like to thank Asbjørn for being the best source of information and help, never a question left unanswered! Robert, we can finally both say that we put the F in FQHE, thanks to our very pleasant collaboration. Thank you for our discussions and for always keeping up with any question I had.

Thank you Lena, Ingrid and Maria for taking care of any problem I had, big or small. Thank you Lars and Jesper for keeping the hardware side of the lab running. On the software side, thank you Rasmus for always being available and helpful. As for people outside the spin-qubit and quantum matter groups, thanks Zhenhai for reminding me to "Smile because being sad won't solve your fabrication problems", and thanks Gunjan, for the emotional boost during writing the thesis. Federico, we've been going through ups and downs a lot during our overlapping time here, thanks for being a person I could discuss with, physics related topics and beyond. As for the rest of QDev, thank you everyone for creating such an amazing and cozy environment, that never gets boring.

A final thank you goes to my friends and family, for putting up with me and supporting me. Fili Stavroula, there were times where you believed more in me than I believed in myself; thank you for your unconditional support!

## Abstract

In this study, we investigate the versatility of complex gate geometry quantum point contacts (QPCs) fabricated on GaAs/AlGaAs heterostructures, for enhanced control and manipulation of electron transport. By carefully designing and optimizing the QPCs, we aim to have precise control over key parameters, including channel length, type of confinement, disorder, and local electron density. This parameter exploration enables us to delve into fundamental phenomena in electron transport and expand our understanding of quantum confinement effects.

The primary objective of this project is to operate these complex QPC devices in the quantum Hall regime and employ them for tunneling experiments. In the quantum Hall regime, QPCs offer the unique capability to locally manipulate edge channels by controlling the tunnelling probability between counter-propagating edge channels. Moreover, the generalization of QPC designs holds promise for their integration as building blocks in more intricate devices, such as interferometers. The ability to fine-tune QPC parameters opens up opportunities for creating complex architectures and exploring novel transport phenomena.

This study focuses on the fabrication and characterization of two main complex gate geometries. By systematically investigating different QPC designs and their associated parameters, our goal is to gain deeper insights into how the confinement potential of QPCs influences their transport properties, especially in the quantum Hall regime. By understanding and controlling electron transport in QPCs, we can harness their potential for improved performance and explore interesting phenomena in the field of quantum devices.

## Contents

| C  | onter | nts                                                | iv        |

|----|-------|----------------------------------------------------|-----------|

| Li | st of | Figures                                            | vi        |

| 1  | Intr  | roduction and Motivation                           | 1         |

| 2  | The   | eory                                               | 4         |

|    | 2.1   | Two-dimensional electron gas                       | 5         |

|    | 2.2   | Conductance quantization in quantum point contacts | 6         |

|    | 2.3   | Quantum Hall effects                               | 9         |

|    |       | 2.3.1 Integer Quantum Hall effect (IQHE)           | 9         |

|    |       | 2.3.2 Fractional Quantum Hall effect (FQHE)        | 13        |

|    | 2.4   | Quantum point contacts in the quantum Hall regime  | 14        |

| 3  | Cor   | nplex Gate Geometry QPC Designs                    | 17        |

|    | 3.1   | $3 \times 3$ design motivation                     | 17        |

|    |       | 3.1.1 First Generation: Single layer design        | 18        |

|    |       | 3.1.2 Second Generation: Swiss cheese design       | 19        |

|    | 3.2   | $3 \times 1$ and $3 \times 2$ designs $\ldots$     | 23        |

|    | 3.3   | Interferometer designs                             | 24        |

| 4  | Ma    | terials, Fabrication and Methods                   | <b>27</b> |

|    | 4.1   | GaAs Material Study                                | 27        |

|    |       | 4.1.1 Gating GaAs                                  | 29        |

|    | 4.2   | Electron Beam Lithography (EBL)                    | 30        |

|    | 4.3   | GaAs fabrication decoded                           | 31        |

|    |       | 4.3.1 From chip to device                          | 31        |

|    |       | 4.3.2 Dose testing gates                           | 35        |

|    | 4.4   | Fridge modifications                               | 37        |

|    | 4.5        | Device characterization at base temperature | 39 |

|----|------------|---------------------------------------------|----|

| 5  | Swi        | ss Cheese QPC characterization              | 40 |

|    | 5.1        | Experimental setup and initial tuning       | 40 |

|    | 5.2        | Results                                     | 43 |

|    | 5.3        | Discussion                                  | 46 |

| 6  | <b>3</b> × | 2 QPC characterization                      | 49 |

|    | 6.1        | Experimental setup                          | 50 |

|    | 6.2        | Results                                     | 51 |

|    |            | 6.2.1 Bulk properties                       | 51 |

|    |            | 6.2.2 Bottom channel                        | 52 |

|    |            | 6.2.3 Top channel                           | 53 |

|    |            | 6.2.4 Middle channel                        | 54 |

|    | 6.3        | Simple QPC results                          | 54 |

|    | 6.4        | Discussion                                  | 55 |

| 7  | Con        | clusions and Outlook                        | 58 |

| A  | Fab        | rication Recipes                            | 60 |

|    | A.1        | Device $SCQPC\emptyset$                     | 60 |

|    | A.2        | Device A3.MF3.LARSER.FQHI_2                 | 66 |

|    | A.3        | Device A1.MF3.LARSER.FQHI_3                 | 71 |

|    | A.4        | Device B1.MF3.EMILYH.QPC                    | 77 |

|    | A.5        | General tips and tricks                     | 82 |

| Bi | bliog      | raphy                                       | 89 |

## List of Figures

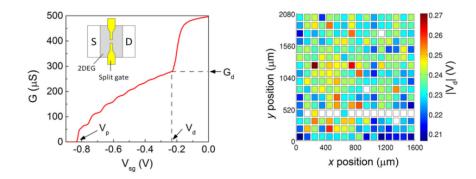

| 1.1 | <ul><li>(a) Conductance across a split gate, as a function of the applied gate voltage on the split gate, inset: how one split gate device looks like.</li><li>(b) Definition voltage extracted from (a), for each of the 256 split gate sites. Figures obtained from [1].</li></ul>                                                                                                                                                                                                                       | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

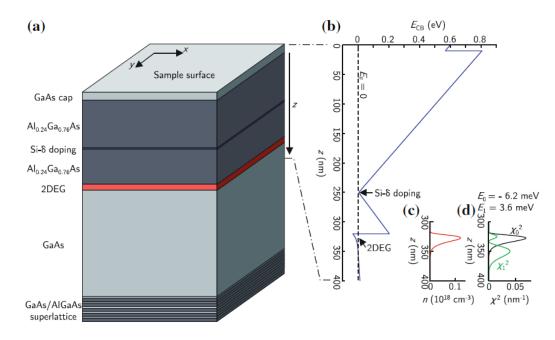

| 2.1 | <ul> <li>(a) Material stack for modulation doped GaAs/AlGaAs heterostructure,</li> <li>(b) Conduction band edge, obtained from numerical self-consistent solution of Schrödinger-Poisson equations,</li> <li>(c) Electron density and (d) square of two lowest energy subband wavefunctions, both as a function of z. Figure adapted from [10]</li> </ul>                                                                                                                                                  | 5  |

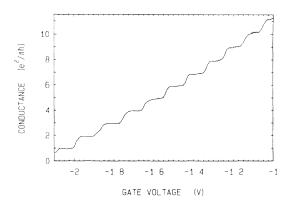

| 2.2 | Conductance quantization in a simple split gate device on GaAs.<br>Figure adapted from [9].                                                                                                                                                                                                                                                                                                                                                                                                                | 6  |

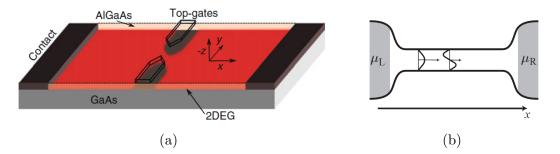

| 2.3 | <ul> <li>(a) GaAs heterostructure, with patterned metallic split gate on the surface. By applying a negative voltage on the split gate, the 2DEG underneath them is depleted, forming a 1D channel, (b) Modelling a QPC as a 1D channel connected to two electron reservoirs. Figure (a) is adapted from [10], while (b) is taken from [11]</li></ul>                                                                                                                                                      | 7  |

| 2.4 | Parabolic dispersion as a function of $k_x$                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8  |

| 2.5 | Integer quantum Hall effect discovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 |

| 2.6 | <ul> <li>(a) Landau levels bend upwards due to the confinement potential of the finite sample. Counterpropagating edge states are formed on both sides of the sample, whenever the Fermi level intersects the LLs.</li> <li>(b) Landau levels broaden because of disorder; the quantum states now comprise of extended states that carry the current through the sample, and localised states. Figures adapted from [15]</li> </ul>                                                                        | 12 |

| 2.7 | Fractional quantum Hall effect. Some integers and fractions are indicated in the longitudinal resistance minima. Adapted from [19].                                                                                                                                                                                                                                                                                                                                                                        | 13 |

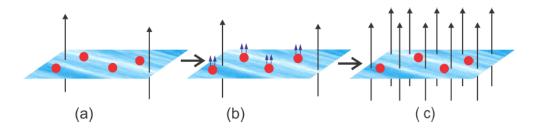

| 2.8 | Deriving the FQHE from the IQHE through composite fermions. (a)<br>Begin with an integer quantum Hall state at $\nu^* = n$ , (b) Attach two<br>magnetic flux quanta to each electron, to convert them to CFs, (c)<br>Spread the flux quanta out to obtain electrons in a higher magnetic<br>field. If the energy gap closes from (b) to (c) then a fractional<br>quantum Hall state at $\nu = n/(2n + 1)$ is formed. All quantities<br>indicated by a star(*) correspond to CFs. Figure adapted from [21]. | 14 |

| 2.9  | Effect of perpendicular magnetic field applied to a QPC, defined in a GaAs 2DEG. Figure adapted from [23]                                                                                                                                                                                                                                                                                                                                                                                               | 15              |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.10 | (a) Bulk parked at $\nu = 2$ , where two edge states exist. (b) As the QPC gates become more negative, backscattering is introduced, (c) One of the edge states is fully backscattered, and the other is fully transmitted. Figure adapted from [15].                                                                                                                                                                                                                                                   | 16              |

| 3.1  | The top left corner shows the device, which is a split gate with an additional center gate, and the data plot shows that for positive center gate voltage, the diagonal resistance converges to the $\nu = 3/2$ state.<br>Figures adapted from [6].                                                                                                                                                                                                                                                     | 18              |

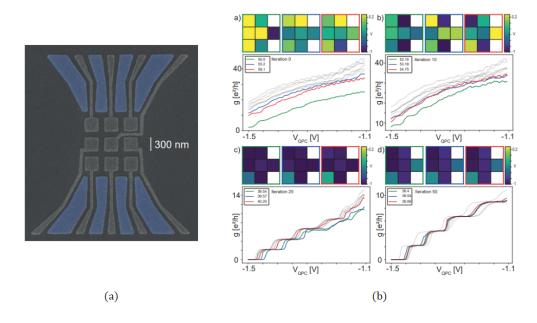

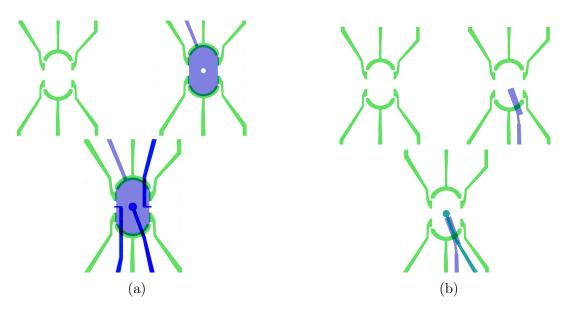

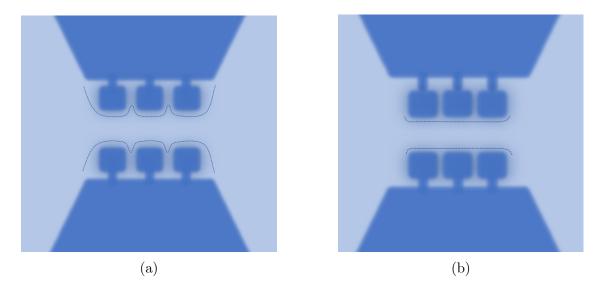

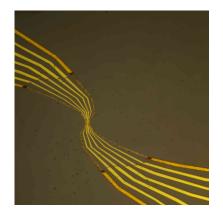

| 3.2  | (a) False color SEM of single layer 3 by 3 design. The blue gates correspond to the outer gates that are negatively biased to form a channel, and the remaining 9 gates are called pixels, (b) Results from applying optimisation algorithm, both (a) and (b) adapted from [25].                                                                                                                                                                                                                        | 19              |

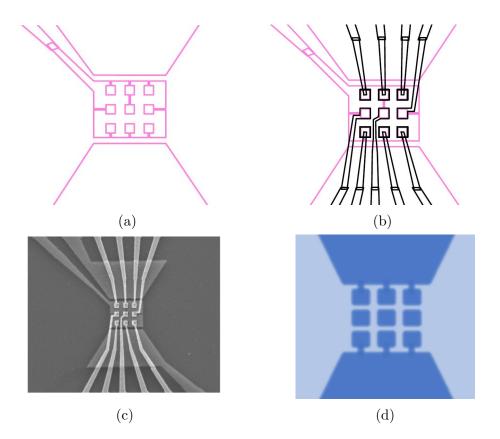

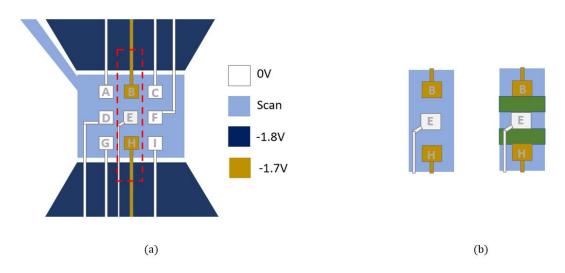

| 3.3  | Swiss cheese design. (a) First gate layer, (b) Full design including<br>both gate layers, (c) SEM of final device, (d) Qualitative picture of<br>how the potential landscape is expected to look like at the 2DEG<br>level, when the outer gates and pixel gates are activated, light blue is<br>free 2DEG and dark blue are areas where the 2DEG is depleted                                                                                                                                           | 21              |

| 3.4  | Demonstration of length, width, density and channel location<br>control in operation. The outer gates (dark blue) are parked at a<br>very negative value to form a big channel. The screening gate<br>(green) is grounded. A white pixel is at 0V, while yellow and red<br>means activated at a negative voltage. (a) Varying the length of the<br>channel, (b) Changing the width, (c) Controlling the density of the<br>channel, (d) Shifting the channel way from the defect/impurity (red<br>star). | 22              |

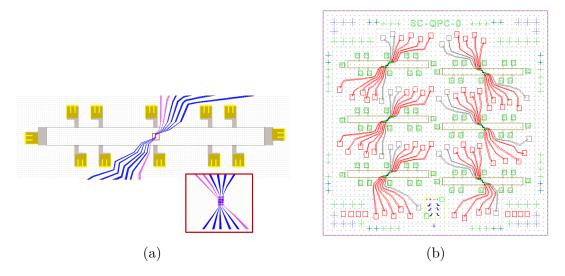

| 3.5  | (a) Isolated Hall bar with Swiss cheese $3 \times 3$ design in the center, (b) SCQPC $\emptyset$ chip layout.                                                                                                                                                                                                                                                                                                                                                                                           | 22              |

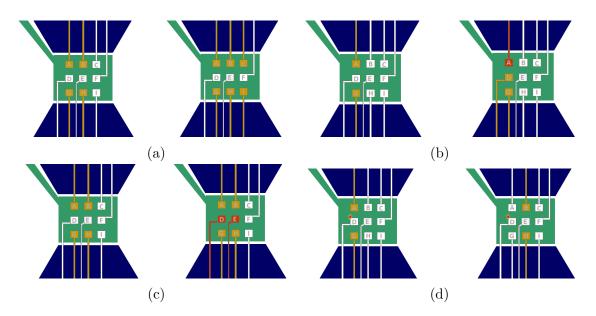

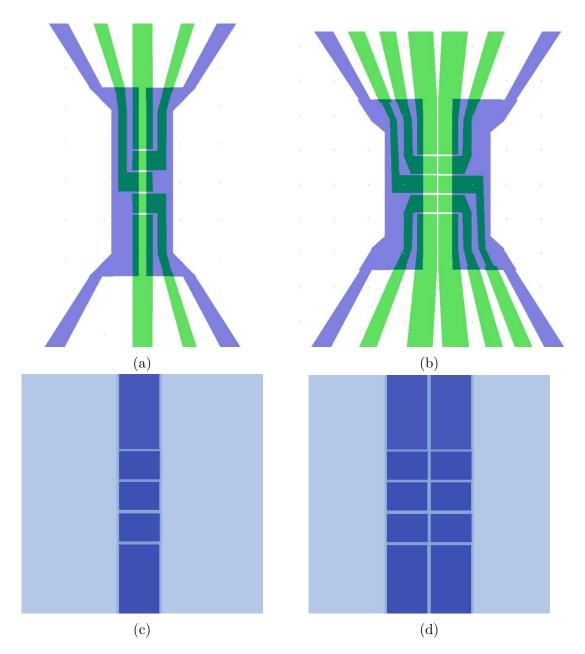

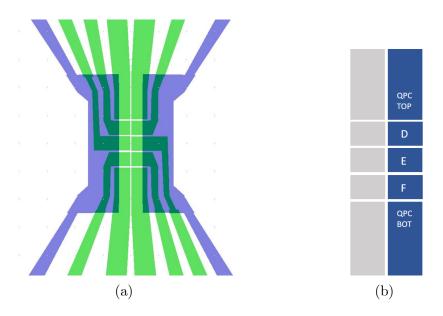

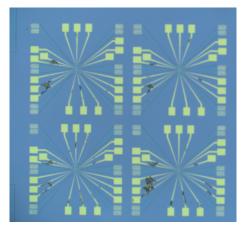

| 3.6  | (a) $3 \times 1$ design and (b) $3 \times 2$ design. In both, the purple gates are<br>in the first layer and green gates are in the second layer, (c) and<br>(d) show an expected qualitative drawing of the potential landscape<br>at the 2DEG level, for devices (a) and (b). Light blue is ungated<br>2DEG and dark blue is when the second layer gates are activated to<br>a negative voltage.                                                                                                      | 24              |

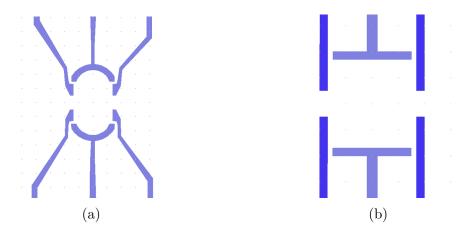

| 3.7  | (a) Single gate layer interferometers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24<br>25        |

| 3.8  | Triple gate layer interferometers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\frac{25}{25}$ |

| 0.0  | 111ph 5au 1ayu muutumuutometto                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20              |

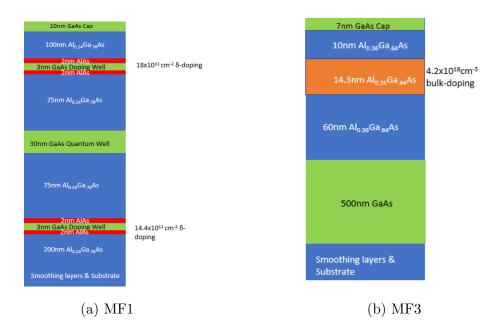

| 4.1  | Two GaAs wafer stacks that were used in this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27              |

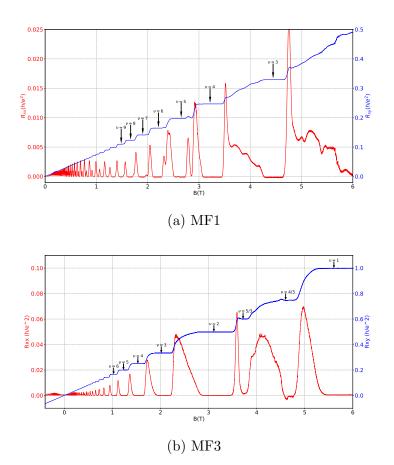

| 4.2  | Hall scans obtained for the two wafers. These measurements were<br>taken as a collaborative effort between the current thesis and thesis                                                                                                                                                                                                                                                                                                                                                                | 0.0             |

|      | [29]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28              |

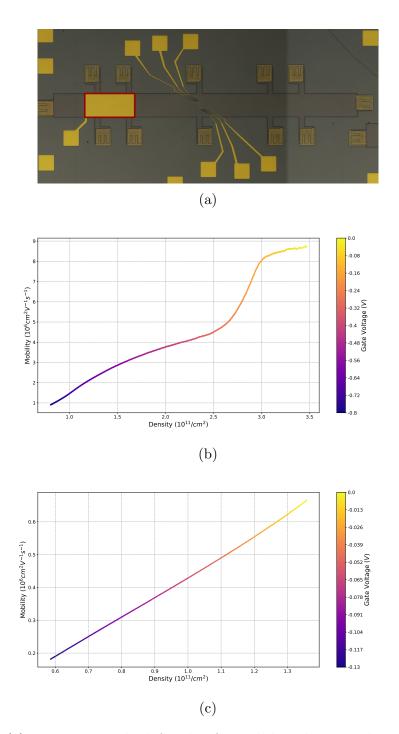

| 4.3  | <ul> <li>(a) Top gate on the left side of a Hall bar shown with a red frame,</li> <li>(b) MF1 wafer, gate effect on electron density and mobility, (c) MF3 wafer, gate effect on electron density and mobility. Figures (b) and</li> <li>(c) were taken as a collaborative effort between the current thesis and thesis [29].</li> </ul>                                                                                      | 29 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

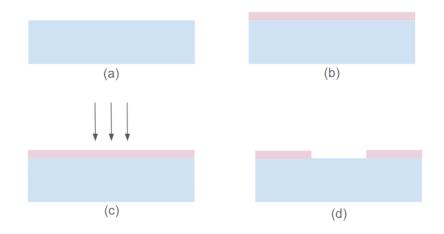

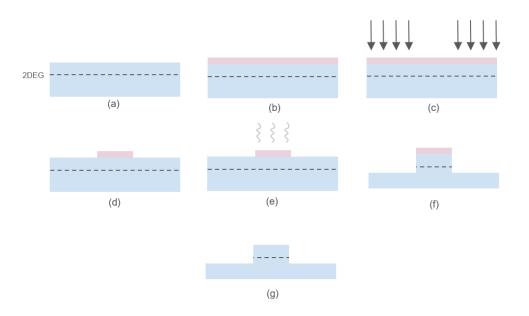

| 4.4  | Steps that repeat for every exposure. Vertical cross section of chip.<br>Blue indicates the substrate and pink is the resist. (a) Clean<br>substrate, (b) Spin suitable resist and bake, (c) Exposure, (d) after<br>development.                                                                                                                                                                                              | 31 |

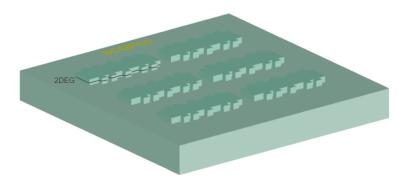

| 4.5  | Chip after mesa etching, here 6 Hall bar mesas are defined. The 2DEG is shown as an example in the top left mesa as a grey line                                                                                                                                                                                                                                                                                               | 32 |

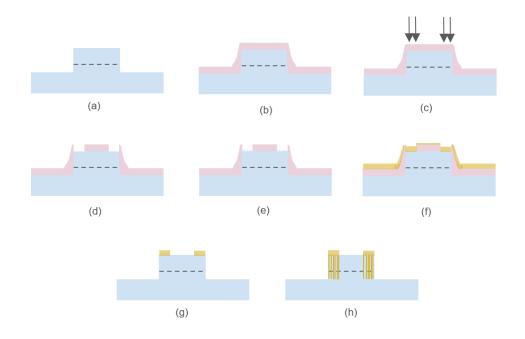

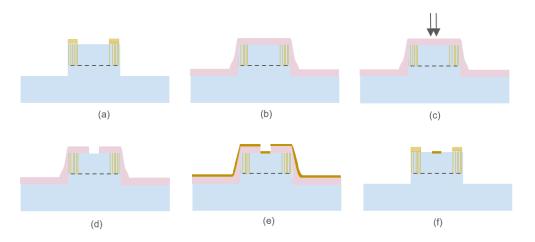

| 4.6  | Defining the mesa steps. Vertical cross section of chip. (a) Starting from a clean chip (blue), (b) spin resist (pink) over the chip and bake, (c) expose areas around the mesa, (d) after development, (e) hard bake, (f) after etch, (g) after stripping resist                                                                                                                                                             | 33 |

| 4.7  | Ohmic Annealing steps. Vertical cross section of chip. (a) starting<br>from a clean substrate (blue) with mesas defined (b) spin resist<br>(pink) over the chip and bake, (c) Expose areas where ohmics will<br>go, (d) after development, (e) after ashing and ion milling, (f) after<br>Ge/Pt/Au evaporation, (g) after stripping the resist (h) after<br>diffusing the ohmics (RTA).                                       | 34 |

| 4.8  | Inner/fine gate patterning. Vertical cross section of chip. (a) starting<br>from a clean substrate (blue), (b) spin resist (pink) over the chip<br>and bake, (c) expose gates, (d) after development, (e) after metal<br>evaporation, (f) After liftoff                                                                                                                                                                       | 34 |

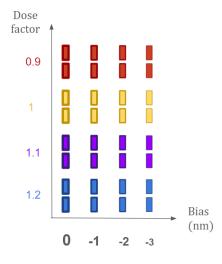

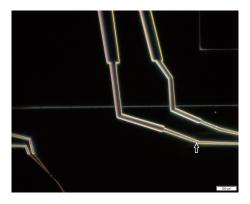

| 4.9  | Dose-Bias array. The vertical axis shows a change in the dose factor<br>in integer steps of 0.1, and the horizontal axis represents the bias in<br>integer steps of -1nm                                                                                                                                                                                                                                                      | 36 |

| 4.10 | (a) Pre-existing RC filters on looms 3 and 4, (b) QDevil copper powder filter connected in series to the existing RC filter on loom 3.                                                                                                                                                                                                                                                                                        | 37 |

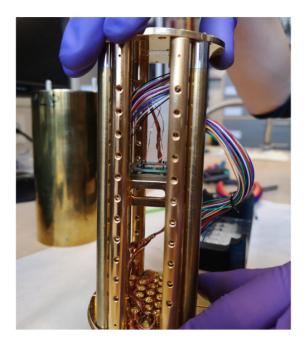

| 4.11 | Copper braid going from the top of the puck which engages to the mixing chamber, to the cavity of the daughterboard.                                                                                                                                                                                                                                                                                                          | 38 |

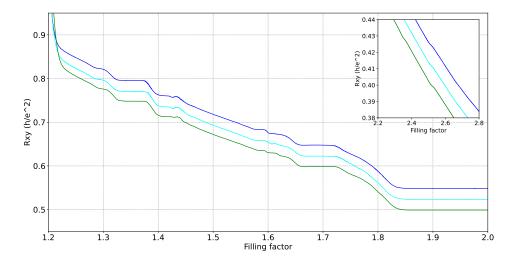

| 4.12 | Hall scan of the same Pfeiffer GaAs chip in T9. Green is with no added filtering, cyan is with copper powder filter added, and blue is with both copper powder filter and a copper braid from the top of the puck to the daughterboard. $R_{xy}$ is shown as a function of the filling factor. Data taken as a collaborative effort between the current thesis and thesis [29]. The curves are vertically shifted for clarity | 38 |

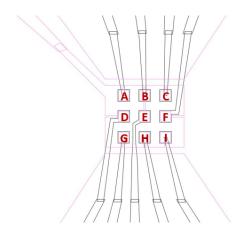

| 5.1  | Device studied in this chapter, the pink gates are in the first layer, and the black gates, the pixels, are in the second layer and renamed as letters between A and I                                                                                                                                                                                                                                                        | 40 |

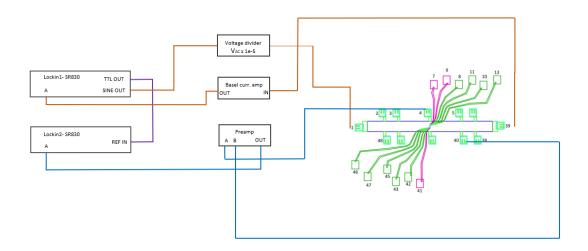

| 5.2 | Voltage biased four point conductance measurement setup. A constant voltage bias is applied between contacts 1 and 39, and the resulting current is amplified and measured. The voltage drop across the device is measured between contacts 4 and 40. The two lockins are slaved to the same frequency                                                                                                                                                                                          | 41 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

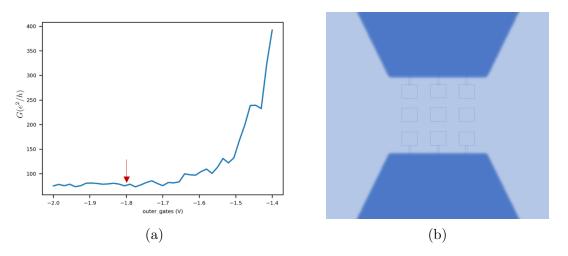

| 5.3 | (a) Park outer gates at their saturation point -1.8V, (b) Qualitative drawing of the 2DEG potential. The 2DEG underneath the outer gates is fully depleted (dark blue), and a channel is formed in between them. Light blue indicates free 2DEG.                                                                                                                                                                                                                                                | 42 |

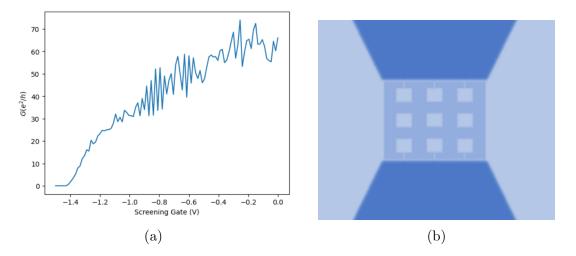

| 5.4 | Figures (b) is a qualitative drawing of the 2DEG potential. Light<br>blue is free 2DEG, dark blue is depleted electron gas and middle<br>blue indicates a potential in between where 2DEG still exists. (a)<br>Screening gate scan corresponding to potential configuration of (b).                                                                                                                                                                                                             | 42 |

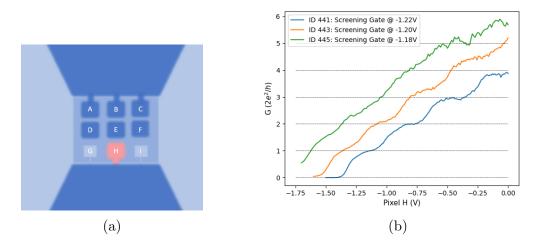

| 5.5 | Figure (a) is a qualitative drawing of the 2DEG potential. Dark blue<br>is depleted 2DEG, medium blue is a voltage in between where 2DEG<br>still exists, light blue is free 2DEG. Pixel H which is being scanned is<br>shown in pink. Pixels A,B,C,D,E,F are saturated, (b) Conductance<br>curve as a function of the voltage on pixel H, for different voltages on<br>the screening gate.                                                                                                     | 43 |

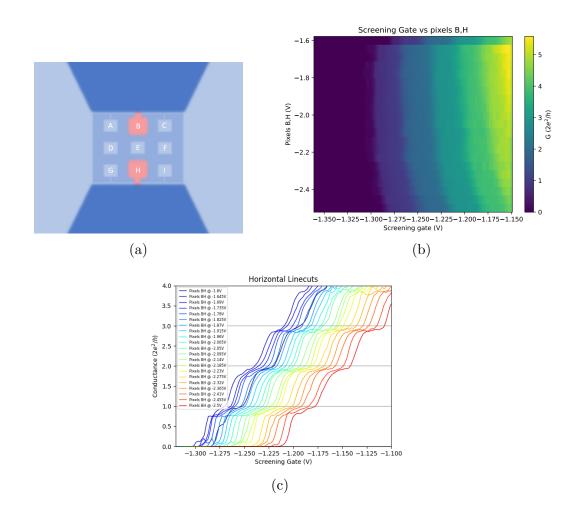

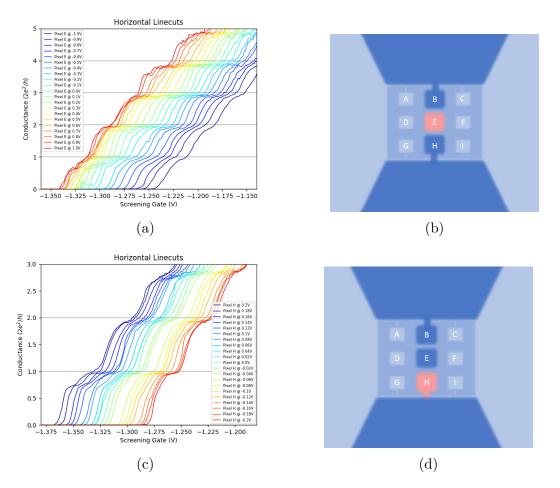

| 5.6 | (a) Qualitative drawing of potential landscape in 2DEG. Dark blue<br>is depleted 2DEG, medium blue is a voltage in between where 2DEG<br>still exists, light blue is free 2DEG, and the gates in pink are being<br>scanned together. Configuration where BH is scanned versus the<br>screening gate, (b) 2D plot of BH pixels versus the screening gate,<br>and the conductance is measured (c) Horizontal linecuts of (b), curves<br>are shifted for clarity.                                  | 44 |

| 5.7 | (a) and (c) are qualitative drawings of the 2DEG potential. Dark blue<br>is depleted 2DEG, medium blue is a voltage in between where 2DEG<br>still exists, light blue is free 2DEG. Pink indicates under which pixel<br>the channel is formed. (a) Screening gate scan for different pixel E<br>voltage values, (b) voltage configuration used for (a). (c) Screening<br>gate scan for different pixel H voltage values, (d) voltage configuration<br>used for (c). The curves are not shifted. | 45 |

| 5.8 | (a) Voltage configuration for the scan shown in 5.7(a). Pixels B and H are depleted, making sure that the only 2DEG that goes from left to right goes between B and H. (b) Focusing on the middle column of the device, the only thing that exists between B and H, is chunks of the screening gate (green) and pixel E.                                                                                                                                                                        | 46 |

| 5.9 | Qualitative drawing of 2DEG potential. Dark blue is depleted 2DEG, light blue is free 2DEG. (a) What happens in the device we measured, because the holes in the screening gate are too far apart, (b) Ideal case, if the screening gate holes were bigger.                                                                                                                                                                                                                                     | 47 |

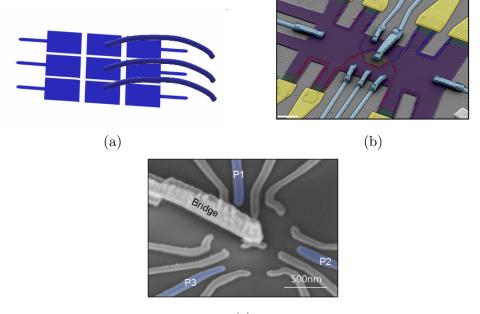

| (a) How air-bridge gates could potentially eliminate the connector problem mentioned in Chapter 3, and keep the $3\times 3$ design single layered, (b) Figure adapted from [34], how bridge gates are used in graphene based devices. (c) Adapted from [35], where an air bridge of dimensions comparable to the ones needed for the $3\times 3$ device is successfully fabricated.    | 48                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) Device under investigation in this chapter, (b) Only the right column is operated, indicated in blue in this qualitative drawing, that shows the gates that the 2DEG is expected to see after screening takes place.                                                                                                                                                               | 49                                                                                                                                                                                                                                                                                                                           |

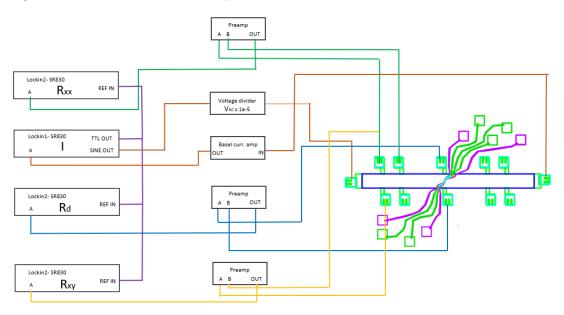

| Voltage biased four point conductance measurement setup. A constant voltage bias is applied between the outer contacts (orange loop), and the resulting current is amplified and measured. Further, the diagonal resistance $(R_d)$ , longitudinal resistance $(R_{xx})$ and transverse resistance $(R_{xy})$ are measured. All four lockins are slaved to the same frequency of 17Hz. | 50                                                                                                                                                                                                                                                                                                                           |

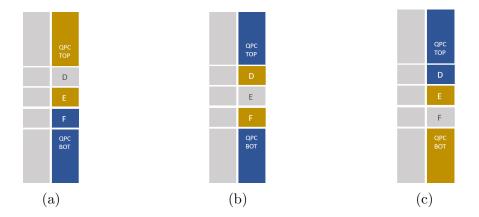

| Laterally shifting the channel, (a) under pixel D (top channel), (b) under pixel E (middle channel), (c) under pixel F (bottom channel). Gray gate means kept at 0V, blue means parked at saturation, -0.5V, and the two yellow gates in each figure indicate the two gates that are used to form a channel between them.                                                              | 50                                                                                                                                                                                                                                                                                                                           |

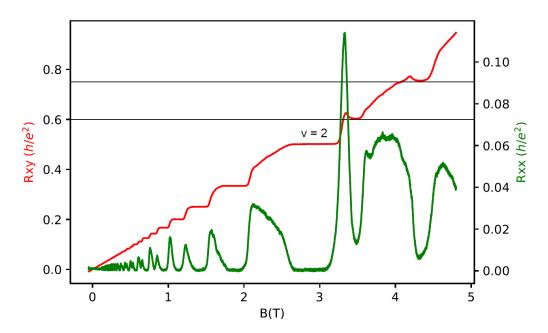

| Hall scan. The $R_{xy}$ curve is drawn in red while the $R_{xx}$ is shown in green.                                                                                                                                                                                                                                                                                                    | 51                                                                                                                                                                                                                                                                                                                           |

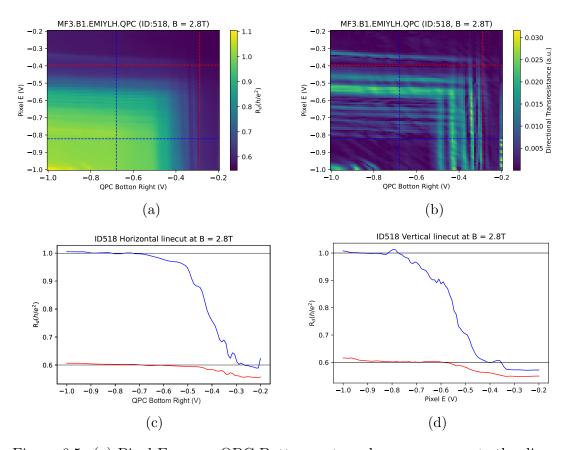

| (a) Pixel E versus QPC Bottom gate, colormap represents the diagonal resistance $R_d$ . (b) Pixel E versus QPC Bottom gate, colormap represents the transresistance, which is the numerical derivative of $R_d$ along the diagonal, (c) Horizontal linecut of (a) along the red and blue horizontal lines, (d) Vertical linecut of (a) along the red and blue vertical lines.          | 52                                                                                                                                                                                                                                                                                                                           |

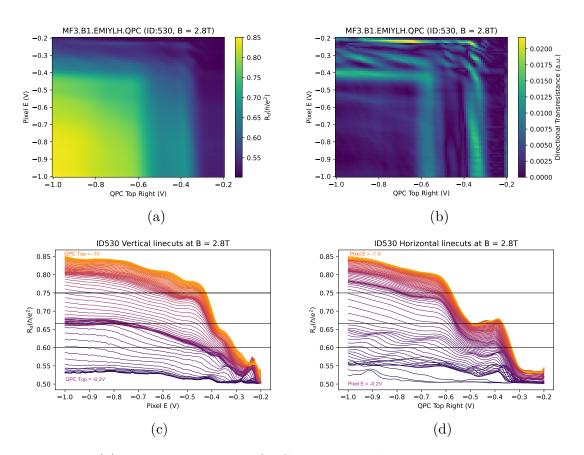

| (a) Pixel E versus gate QPC top gate, colormap represents the diagonal resistance $R_d$ . (b) Pixel E versus gate QPC top gate, colormap represents the transresistance, numerical derivative of (a) along the diagonal, (c) Vertical linecuts of (a), (d) Horizontal linecuts of (a).                                                                                                 | 53                                                                                                                                                                                                                                                                                                                           |

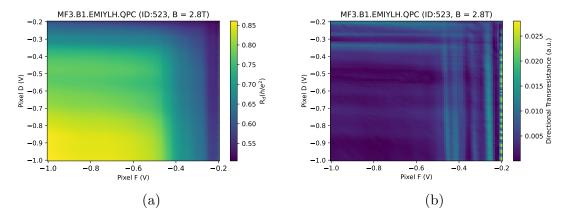

| (a) Pixel D versus pixel F, colormap represents the diagonal resistance $R_d$ . (b) Pixel D versus pixel F, colormap represents the transresistance, numerical derivative of (a) along the diagonal                                                                                                                                                                                    | 54                                                                                                                                                                                                                                                                                                                           |

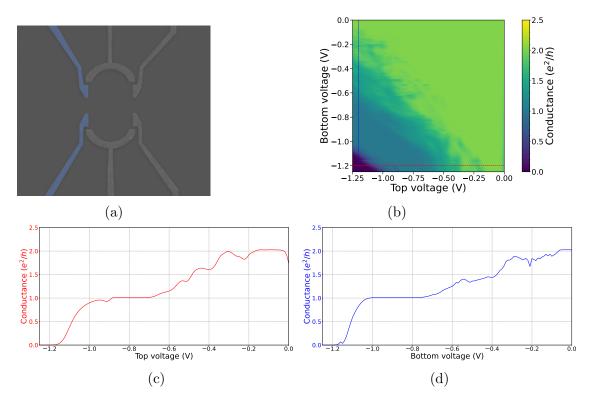

| (a) Interferometer device fabricated on the same material as the $3 \times 2$ device of Figure 6.1. We use the left QPC shown in blue. (b) Diagonal conductance $G_d$ as a function of the top and bottom QPC gates, (c) and (d) are linecuts of (b) along the red and blue lines.                                                                                                     | 55                                                                                                                                                                                                                                                                                                                           |

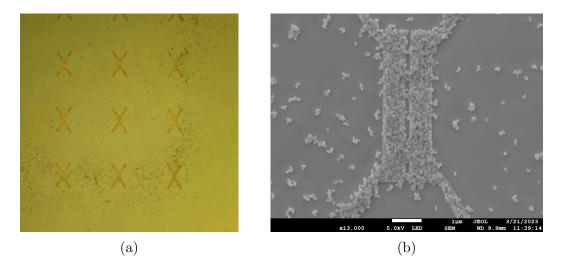

| $HfO_2$ dots caused by oxide layer deposition between the first and                                                                                                                                                                                                                                                                                                                    | 55                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                        | problem mentioned in Chapter 3, and keep the $3\times 3$ design single<br>layered , (b) Figure adapted from [34], how bridge gates are used in<br>graphene based devices. (c) Adapted from [35], where an air bridge<br>of dimensions comparable to the ones needed for the $3\times 3$ device is<br>successfully fabricated |

| A.1 | Mesa etchant preparation timing                                                                                     | 62 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| A.2 | Example of how under-developed resist looks like in dark field $\ldots$ .                                           | 84 |

| A.3 | Gold from second layer fine gates evaporation sticking on the sides of<br>the first layer outer gates after liftoff | 84 |

| A.4 | Outer gates climbing mesa                                                                                           | 85 |

| A.5 | How the ALD dots aka popcorns look like. They are not only localized around the gates, they span several microns.   | 87 |

## Chapter 1

## Introduction and Motivation

A good introduction to the motivation for this thesis project would be the statistical study carried out in [1]. Here, the researchers investigate the conductance properties of one-dimensional (1D) quantum wires. More specifically, they studied transport through 256 nominally identical split gates fabricated on the same GaAs/AlGaAs heterostructure chip. By using two multiplexers, they were able to isolate each of these split gates, and measure its transport properties. An important thing to note down is that all of these devices were measured in the same cooldown, under the same experimental conditions. Despite the devices being nominally identical, <sup>1</sup> and measured in exactly the same way and conditions, they did not exhibit the same behaviour.

Even though the main focus of this work is centered around variations in the 0.7 anomaly among these split gates, we can come to some important conclusions regarding the parameters that influence the transport properties of this ensemble of devices.

The researchers initially measured the 1D conductance curve for every split gate, as shown in Figure 1.1(a), and noted down two critical voltages for each channel, the definition voltage  $V_d$ , and the pinch off voltage  $V_p$ . The definition voltage  $V_d$ , is the gate voltage where the system goes from being two-dimensional (2D) to 1D and the ballistic channel is formed. The pinch off voltage is the voltage at which the split gate fully blocks the channel. Intuitively, we understand that both  $V_d$  and  $V_p$ must depend on the local electron density [2]. If the density is higher, the definition voltage would be more negative, as we would need to push harder to get rid of the extra electrons underneath the gates, and vice versa. Indeed the relation between the definition voltage and the electron density  $n_{2D}$  is the following:

$$|V_d| = \frac{edn_{2D}}{\epsilon} \tag{1.0.1}$$

where e is the electron charge, d is the distance from the surface to the 2DEG

<sup>&</sup>lt;sup>1</sup>All devices went through the same fabrication process, the design is the same, consequently they are expected to be nominally identical up to nanoscale variations due to fabrication.

and  $\epsilon$  is the permittivity of the material between the surface and the 2DEG. A similar argument goes for the pinch off voltage. As seen in Figure 1.1(b), the definition voltage (and consequently the local electron density because of equation 1.0.1) varies significantly between the different split gate sites.

Figure 1.1: (a) Conductance across a split gate, as a function of the applied gate voltage on the split gate, inset: how one split gate device looks like. (b) Definition voltage extracted from (a), for each of the 256 split gate sites. Figures obtained from [1].

The main observation is that the devices exhibit different electrostatic behaviour, and this is primarily attributed to variations in the local 1D potential of each split gate. Several factors could contribute to the variability of the 1D potential among these devices, including nanoscale variations due to fabrication, or the presence of impurities and defects inside the channel.

The crucial aspect that motivates our work, is that not only the electrostatics, but more importantly the transport properties of QPCs are highly dependent on the specific characteristics of the 1D potential. We realize that numerous parameters play a role in determining the 1D potential. It follows naturally that we seek methods to manipulate these parameters, granting us ultimate control over the 1D potential profile of a ballistic channel.

A few groups have focused their efforts on doing that by adding gate complexity to their designs, to study the dependence of QPC transport properties to specific parameters. Some of these include the length [3], [4], potential shape [5] and local electron density of the channel [6]. It is worth noting that only recently have advances in electron beam lithography and deposition tools in academic cleanrooms enabled multi-layer complex gate geometries, with unprecedented control over the 2DEG potential.

One of the reasons why we would like to gain ultimate control over the potential, is to be able to shape it in a regime of interest, where some interesting phenomena appear. This could be to study many body physics effects such as the 0.7 anomaly, the zero bias anomaly or even realizing even denominator fractional quantum Hall states in the constriction. Such effects have proven to be sensitive to the specifics of the QPC potential. In this work, we test two different complex gate geometry QPC<sup>2</sup> designs, which are fabricated on GaAs/AlGaAs heterostructures. With our designs, we opt to control parameters such as the length of the channel, the width of the constriction, as well as the type of confinement, the location of the channel (to have the ability to shift the constriction around in real space to avoid a possible defect or impurity), and finally the local electron density of the channel. By obtaining control over these parameters, one could study the phenomena mentioned above in much greater detail and extent.

A second reason as to why QPCs need to be generalized, is to use them as building blocks in more complex devices such as interferometers. In the quantum Hall regime, a QPC can locally manipulate edge channels by controlling the tunnelling probability between counter-propagating edge channels. The ultimate goal for this project is to operate our complex QPC devices in the quantum Hall regime and perform such tunneling experiments.

Chapter 2 provides an exploration of the theory surrounding quantum point contacts, the integer and fractional quantum Hall effects, and their combined study where QPCs are operated within the quantum Hall regime. This is followed by Chapter 3, which motivates and describes the two main designs that were fabricated and characterized in this thesis. These designs consist of the  $3 \times 3$  pixelated channel design, as well as two simplified versions, that share similar properties to the  $3 \times 3$ . These are called the  $3 \times 1$  and  $3 \times 2$  designs.

In Chapter 4, we take a brief detour to delve into the technical aspects of this work, looking into the basics of fabrication and discussing some experimental methods. Finally, Chapters 5 and 6 present the measurement results obtained during the characterization of the designs mentioned in Chapter 3, providing an analysis of their properties.

<sup>&</sup>lt;sup>2</sup>Or 1D ballistic channel geometries in the variable length case.

## Chapter 2

## Theory

"Semiconductor technology has developed considerably during the past several decades. [...] One key ingredient of the LSI technology is the development of the lithography and microfabrication. The current minimum feature size is already as small as  $0.2\mu m$  [...]. The next generation of devices is highly likely to show unexpected properties due to quantum effects and fluctuations"

These words were written 25 years ago [7]. The advancements in science and technology that happened ever since are impressive. Today, the minimum feature size that one can achieve with lithographic techniques has dropped to sub 10 nm, allowing us to probe physics that was inaccessible back then.

The combination of modern lithographic technology, and advancements in semiconductor heterostructure crystal growth technologies such as MBE, have produced a playground of very interesting structures that include quantum wires, quantum dots, antidots, interferometers and Quantum Point Contacts (QPCs). In such mesoscopic devices as they are called, the feature sizes are small<sup>1</sup>, and we cannot deny the wavelike nature of electrons anymore. A number of fundamental quantum effects originate from this wavelike nature of electrons. For instance, there is the Aharonov-Bohm effect, the quantum Hall effects, and most importantly for us in this thesis is the quantization of conductance in integer steps of  $2e^2/h$ .

We are interested in systems where one can define a one-dimensional ballistic channel or a QPC. There are many platforms available to study QPCs, a relatively more novel example being graphene [8], but more relevant to this thesis is the two-dimensional electron gas of a GaAs/AlGaAs heterostructure, where QPCs where first demonstrated, i.e. [9].

<sup>&</sup>lt;sup>1</sup>Small enough to obey quantum mechanics, but not atomic physics.

#### 2.1 Two-dimensional electron gas

An important system where quantum effects can be observed is the two-dimensional electron gas (2DEG). There are two basic systems where 2DEGs are realized. One of them is the Si MOSFET (Metal Oxide Semiconductor Field-Effect Transistor). The other system, which is highly utilized in this work, is modulation doped GaAs/AlGaAs heterostructures, where an electron quantum well is formed close to the interface of these two materials. Note that 2DEGs of the latter kind represent the cleanest solid state platform available to experimentalists<sup>2</sup>.

Figure 2.1: (a) Material stack for modulation doped GaAs/AlGaAs heterostructure, (b) Conduction band edge, obtained from numerical self-consistent solution of Schrödinger-Poisson equations, (c) Electron density and (d) square of two lowest energy subband wavefunctions, both as a function of z. Figure adapted from [10].

Suppose as in Figure 2.1(a), we have a type I <sup>3</sup> heterointerface, where the material on top is AlGaAs, and the bottom one is intrinsic GaAs. In combination with this heterointerface, a technique called modulation doping is used. A sheet (or thin volume) of Si donors is placed in the AlGaAs side, at a distance from the heterointerface between the two semiconductors. Because of the conduction band offset, it is energetically favorable for the donor electrons to move away from the AlGaAs side which has a bigger band gap, to the GaAs side with the smaller band gap.

Therefore, an internal electric field will be created, and directed from the non-neutralized donors in the AlGaAs to the additional electrons in the GaAs. This field is also responsible for the band bending shown in Figure 2.1(b). This

<sup>&</sup>lt;sup>2</sup>According to [10] published in 2015.

<sup>&</sup>lt;sup>3</sup>As defined in [11].

continues until equilibrium is reached, where the Fermi levels line up. During this process, a triangular quantum well is formed in the GaAs layer. The electrons that are trapped in this potential well form the 2DEG, and should have a very high mobility in the x-y plane, since they move within the GaAs which is free of dopant impurities <sup>4</sup>. Evidently, electron mobilities in GaAs/AlGaAs are very high compared to MOS structures. Furthermore, by patterning metallic gates on the surface of such heterostructures, one can electrostatically control the shape of the 2DEG, as we will see in the following section.

## 2.2 Conductance quantization in quantum point contacts

QPCs are fundamental building blocks for many experiments in mesoscopic physics, not to imply that they are not interesting systems on their own; quite the opposite. One way to experimentally realize them is in 2DEGs. The 2DEGs that this work is based on are formed in GaAs/AlGaAs heterostructures. To form the simplest QPC, it is necessary to pattern two metallic gates on the surface of the heterostructure, forming a split gate structure shown in Figure 2.3(a). By applying a negative voltage on this pair of gates, the 2DEG underneath them is depleted from electrons, and what remains is a narrow channel connecting two large electron reservoirs. In 1988, two independent groups, Wharam et.al [12] and van Wees et al. [9], studied QPCs for the first time using a split gate in a GaAs 2DEG, at zero magnetic field. It was a surprising result that the conductance showed a step like behaviour, being quantized in integer steps of  $2e^2/h$  with respect to the applied gate voltage on the split gate, as depicted in Figure 2.2.

Figure 2.2: Conductance quantization in a simple split gate device on GaAs. Figure adapted from [9].

More than 30 years have passed since the first realization of QPCs, and they are still widely used and studied in experiments. In this section, we discuss the transport properties of a QPC at zero magnetic field, and see how a simple

<sup>&</sup>lt;sup>4</sup>It is well known that impurity scattering is one of the main limiting factors in carrier mobility, especially in low temperatures.

non-interacting electron model can explain the conductance quantization. Before continuing, I should warn that this non-interacting electron model is not sufficient to explain everything. Some anomalies appear in the conductance, such as the famous 0.7 anomaly (see Figure 2.2), and cannot be described within this model. Electron-electron interactions need to be considered, and a sufficient explanation about the origin of this effect is still lacking. Some experimental attempts that utilize more complex QPC structures to study the 0.7 anomaly are found in [5], [4].

Figure 2.3: (a) GaAs heterostructure, with patterned metallic split gate on the surface. By applying a negative voltage on the split gate, the 2DEG underneath them is depleted, forming a 1D channel, (b) Modelling a QPC as a 1D channel connected to two electron reservoirs. Figure (a) is adapted from [10], while (b) is taken from [11].

We can model a quantum point contact as a one dimensional channel that connects two electron reservoirs, with corresponding chemical potentials  $\mu_L$  to the left and  $\mu_R$  to the right, as depicted in Figure 2.3(b).

To observe conductance quantization, the first condition is that the channel should be sufficiently narrow. In other words, the width should be comparable to the Fermi wavelength for electrons,  $w \sim \lambda_F$ , such that quantization can occur in the y-direction indicated in Figure 2.3(a). The number of transverse quantized modes that can fit in the channel at any given width, is exactly equal to the integer N that precedes the conductance quantum of  $2e^2/h$ .

$$G = N \frac{2e^2}{h} \tag{2.2.1}$$

With the first condition we satisfy the 1D in 1D ballistic transport. To also satisfy the word ballistic, the electrons need to travel without any energy loss in the x-direction. This brings us to the second condition, which is that the mean free path of electrons  $l_e^5$ , must be much larger than the length of the channel,  $L \ll l_e$ , such that electrons travelling from one reservoir to the other will not experience any inelastic collisions inside the wire.

The following ansatz is considered for the wavefunction [11]:

<sup>&</sup>lt;sup>5</sup>The average distance an electron can travel before scattering off impurities or defects.

$$\psi_{n,\mathbf{k}}(\mathbf{r}) = \chi_n(y) \frac{1}{\sqrt{L}} \exp^{ik_x x}$$

(2.2.2)

In equation 2.2.2, condition one for quantization in the y-direction is represented by the transverse modes of the wire  $\chi_n(y)^6$ . The second condition of long mean free path is included in the assumption that the x-direction is infinitely long, and electrons travel as plane waves. The energy dispersion along the x-direction is assumed to be parabolic:

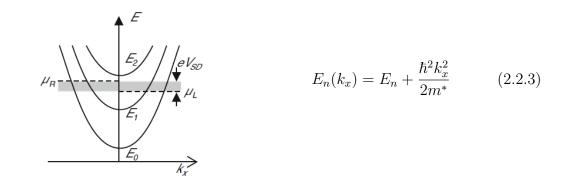

Figure 2.4: Parabolic dispersion as a function of  $k_x$ .

where  $E_n$  is the energy of the n<sup>th</sup> subband due to quantization in the y-direction. Suppose a voltage bias  $|e|V_{SD} = \mu_R - \mu_L$  is applied between the left and right electron reservoirs. In this case, only the electrons with  $k_x$  inside the bias window will contribute to the current. Electrons originating from the reservoir to the left have a positive  $k_x$  and are called right movers, and similarly electrons coming from the right reservoir are left movers owning to their negative  $k_x$ . The goal is to calculate the current through the wire, created by the movement of these energetically available electrons.

The differential current density of mode n and wavevector  $k_x$  is written as:

$$d\mathbf{j}_{n,k_x}(\mathbf{r}) = -\mathbf{\hat{x}}g_s \frac{|e|}{h} |\chi_n(y)|^2 \frac{\partial E_n(k_x)}{\partial k_x} dk_x$$

(2.2.4)

where  $g_s$  denotes spin degeneracy. To obtain the total current through the wire, we need to integrate over the left and right movers that are energetically allowed to move because they are included in the bias window. Note that a summation is also performed over all occupied modes n.

$$I_{tot} = \left(\sum_{n_{occ}} \int_{k_x > 0} d\mathbf{j}_{n,k_x}\right) - \left(\sum_{n_{occ}} \int_{k_x < 0} d\mathbf{j}_{n,k_x}\right)$$

(2.2.5)

<sup>&</sup>lt;sup>6</sup>More strictly the term  $\chi_n(y)$  should be  $\chi_n(y, z)$  since we also have confinement in the z direction, however for simplicity let us assume that  $\mathbf{r} = x\hat{x} + y\hat{y}$ , since the z and x-y Hamiltonians are separable.

The electron reservoirs are described by the Fermi-Dirac distribution. Since the electrons that create the current originate from these reservoirs, they also obey the Fermi-Dirac distributions  $f_R$ ,  $f_L$  of their corresponding mother reservoir. The integrals in 2.2.5 can be re-written with the integration to be over energy.

$$I_{tot} = g_s \frac{|e|}{h} \left( \sum_{n_{occ}} \int_{E_n}^{\infty} dE \left[ (f_L(E - \mu_L) - f_R(E - \mu_R)) \right] \right)$$

(2.2.6)

Finally, in the linear regime where the applied source-drain bias is very small  $(|e|V_{SD} \ll K_BT)$ , the spin degeneracy is two, and at the zero temperature limit we come to the formula for conductance quantization.

$$G = \frac{I_{tot}}{V_{SD}} = 2\frac{e^2}{h}N, \qquad T \to 0$$

(2.2.7)

All the above are valid for transmission through an ideal quantum wire. Due to simplified assumptions, the energy eigenvalues  $E_n$  were independent of the spatial distribution of the wire. Realistically, this is not the case. Both the width and confinement potential are dependent on x, and the solutions to the Schrödinger equation become more complex. Now for the electrons in the bias window, there is a finite probability of transmission and reflection through the QPC. For both the left and right movers, there is a probability of transmission through the QPC,  $T_n(E)$  and a corresponding probability for reflection  $1 - T_n(E)$ . After taking this into account, we come to another form for 2.2.7, the Landauer formula. Proof of equation 2.2.8 can be found in several textbooks [11],[10].

$$G = \frac{I_{tot}}{V_{SD}} = 2\frac{e^2}{h} \sum_{n} T_n(E_F), \qquad T \to 0$$

(2.2.8)

#### 2.3 Quantum Hall effects

#### 2.3.1 Integer Quantum Hall effect (IQHE)

"The birthday of the quantum Hall effect can be fixed very accurately. It was the night of the 4th to the 5th of February 1980 around 2 a.m. during an experiment at the High Magnetic Field Laboratory in Grenoble." [13]

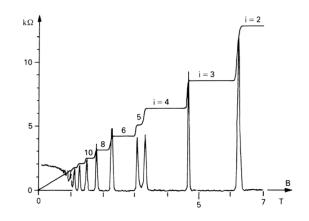

Klaus von Klitzing's research at the time included characterization of the electronic transport of silicon field effect transistors. For this, Hall bar devices were provided by G.Dorda and M. Pepper. These 2DEG systems were cooled down to 4.2K and exposed to high magnetic fields [14]. The result can be summarized in one of the most famous experimental curves in condensed matter physics:

Figure 2.5: Integer quantum Hall effect discovery.

The transverse (or Hall) resistance exhibits a steplike behaviour at higher fields,

$$\rho_{xy} = \frac{1}{\nu} \frac{h}{e^2} \tag{2.3.1}$$

where  $\nu$  is an integer ( $\nu = i$  in Figure 2.5). In the magnetic field regions where plateaus occur in  $\rho_{xy}$ , the longitudinal resistance  $\rho_{xx}$  settles to zero. Because of the two dimensional nature of the system, the resistance and conductance become  $2 \times 2$ tensors. One can show that whenever the field value is such that the Hall resistance is parked on a plateau  $\nu$ , the transverse Hall resistance and conductance are both zero simultaneously,

$$\rho_{xx} = \sigma_{xx} = 0, \quad \text{if } \rho_{xy} \neq 0 \tag{2.3.2}$$

Vanishing conductance is characteristic of an insulating state. In turn, we would call a material with zero resistance a perfect conductor. We see that our intuition is not very helpful when trying to understand the high magnetic field behaviour of a 2DEG.

In the following, we will study the IQHE through the edge state picture. When the system has finite dimensions  $L_x \times L_y$ , it is found that the current going through the system is carried by counter-propagating edge states that intersect the Fermi level.

In the low magnetic field limit, in-plane electrons move in circles due to the perpendicular magnetic field. As the magnetic field is further increased, there is a point where an electron will only be able to perform few circles before scattering and losing all of it's momentum ( $\omega_c \tau \gg 1$ ). The kinetic energy of the electron will then become quantized into discrete energy levels; the so-called Landau levels. To calculate them, one has to solve the Schrödinger equation for an electron in an external magnetic field:

$$\left(\frac{(\mathbf{p}+|e|\mathbf{A})^2}{2m^*}\right)\psi(x,y) = E\psi(x,y)$$

(2.3.3)

Typically, a Landau gauge is chosen for the vector potential,  $A_y = Bx\hat{y}$ . Because the Hamiltonian commutes with the momentum operator in the y direction, we can consider an Ansatz solution of the following form for the wavefunction:

$$\psi_k(x,y) = e^{iky} f_k(x) \tag{2.3.4}$$

The eigenvalue problem takes the final form:

$$\left(\frac{p_x^2}{2m^*} + \frac{1}{2}m^*\omega_c^2\left(x + \frac{\hbar k}{|e|B}\right)^2\right)f_k(x) = Ef_k(x)$$

(2.3.5)

This Hamiltonian corresponds to a shifted harmonic oscillator in the x-direction, with oscillation centers  $x_0 = -\hbar k/|e|B$ . The eigenenergies of the problem represent the Landau levels, and are given by:

$$E_n = \hbar\omega_c (n + \frac{1}{2}) \tag{2.3.6}$$

where n = 0, 1, 2... is the Landau level index. The wavefunction is described by the wavevector k. The Landau level energies are independent of k, this makes them highly degenerate. The degeneracy of the Landau levels  $n_L$ , is equal to the number of flux quanta that pierce through the system:

$$n_L = N_\Phi = \frac{\Phi}{\Phi_0} \tag{2.3.7}$$

where  $\Phi_0 = h/e$  is defined as the flux quantum. Finally, the filling factor represents the ratio between the number of electrons in the system divided by the number of flux quanta:

$$\nu = \frac{N_e}{N_\Phi} \tag{2.3.8}$$

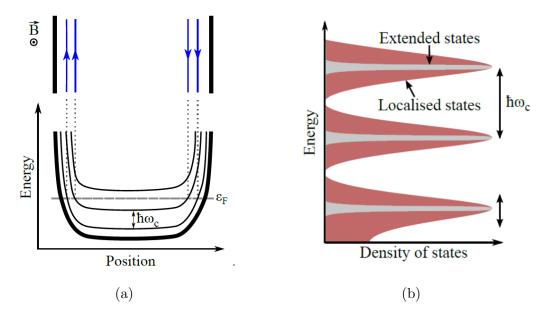

The Landau level description ignores the existence of physical boundaries, however the resistance behaviour observed in Figure 2.5 is a consequence of the system having a finite size. The confining potential causes the Landau levels to bend upwards towards the edge of the sample as shown in Figure 2.6(a).

Whenever the Fermi level lies in between two Landau levels, the bulk is insulating due to the presence of the gap in the bulk  $\hbar\omega_c$ . The edges on the other hand show a completely different behaviour. Because of the Landau level bending, each level that is below the Fermi level crosses the Fermi energy twice, once on each side of the sample. These two intersection points represent 1D conducting channels that emerge at the edges of the system. These two edge channels for each LL are counterpropagating at the opposite sides of the sample, and as they are separated by a macroscopic distance, backscattering is entirely absent. Since the bulk is insulating, no current can run through it, and in the edge picture, the current can only run through these edge channels.

The question we have answered so far is: Why do the  $R_{xy}$  plateaus have the integer value that they do? It is because that integer value corresponds to the number of LLs that intersect the Fermi energy, which in turns corresponds to how many conducting edge channels exist in the system. However, this picture does not

explain why resistance exhibits plateaus; and why these plateaus extend over a range of magnetic field. To understand this we need to consider how disorder influences the system.

Figure 2.6: (a) Landau levels bend upwards due to the confinement potential of the finite sample. Counterpropagating edge states are formed on both sides of the sample, whenever the Fermi level intersects the LLs. (b) Landau levels broaden because of disorder; the quantum states now comprise of extended states that carry the current through the sample, and localised states. Figures adapted from [15].

We start from a free 2DEG, characterized by a continuous density of states (DOS), resembling that of a metal. Subsequently, we introduce a perpendicular magnetic field; this results in the DOS to become discrete, forming the LLs, which at a first glance are assumed to be flat. However, this assumption does not accurately reflect the complexity of the system in reality. Our samples are inherent to random disorder, and in the presence of such disorder, the energy spectrum of the LLs broadens. The quantum states of the system now comprise of extended and localised states. Extended states spread through the sample, and carry the current across the device. Localised states on the other hand are, well, localised. They are restricted in some small region in space, usually trapped around maxima or minima of the spatial potential that varies within the sample. Since these states cannot move, they do not contribute to the current.

To understand how the plateaus are formed, consider the following: Suppose that all extended states in a given LL are filled, and the magnetic field is decreased, with fixed electron density in the system. The degeneracy of the LLs decreases, but rather than jumping to the next LL, localised states in the tails of the DOS curve are populated. Since these states do not contribute to the current, the resistance or conductance does not change over a range of magnetic field, until the next extended states are reached. For more details on the IQHE the reader is referred to [16] as a qualitative source, and [17] for a deeper mathematical approach.

#### 2.3.2 Fractional Quantum Hall effect (FQHE)

The fractional quantum Hall effect (FQHE), much like the IQHE, emerges in two-dimensional electron systems subject to a strong perpendicular magnetic field at low temperatures. The difference between the IQHE and FQHE is that electron-electron interactions become important in the latter.

The strong interactions originate from the Coulomb repulsion between electron. Under normal circumstances, this interaction is weak, and the electrons behave as non-interacting particles. In strong magnetic fields, the interaction energy between electrons becomes comparable to their kinetic energy. The strong interactions lead to the formation of correlated states, where the electrons organize themselves collectively to minimize the overall energy of the system. These correlated states are characterized by the appearance of energy gaps, which correspond to the incompressible states observed in the FQHE.

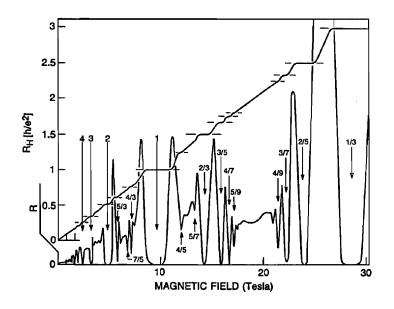

In their experimental observations, the IQHE and FQHE are identical, except for the value of the quantized Hall resistance  $R_{xy} = h/fe^2$ , with the difference being that f is now a fraction. In 1982, Tsui, Stormer and Gossard [18] exposed their 2DEG to very high magnetic fields, aiming to force all electrons to the lowest LL. With their kinetic energy being quenched, it would be entirely the Coulomb repulsion determines their state.

Figure 2.7: Fractional quantum Hall effect. Some integers and fractions are indicated in the longitudinal resistance minima. Adapted from [19].

One theoretical framework used to explain the FQHE is the composite fermion (CF) model proposed by Jain [20].

"The motivation for the CF theory came from the following observation: If you mentally erase all numbers in Fig. 1 (Figure 2.7 for us), you will notice that it is impossible to tell the FQHE from the IQHE." [21]

In this proposed unifying framework, each electron in the 2DEG binds to two magnetic flux quanta, transforming it into a composite particle, or a "composite fermion" (CF). In other words, it is suggested that fractional quantum Hall effect electrons can be understood as a manifestation of the integer quantum Hall effect of composite fermions.

Figure 2.8: Deriving the FQHE from the IQHE through composite fermions. (a) Begin with an integer quantum Hall state at  $\nu^* = n$ , (b) Attach two magnetic flux quanta to each electron, to convert them to CFs, (c) Spread the flux quanta out to obtain electrons in a higher magnetic field. If the energy gap closes from (b) to (c) then a fractional quantum Hall state at  $\nu = n/(2n + 1)$  is formed. All quantities indicated by a star(\*) correspond to CFs. Figure adapted from [21].

The intuitive idea that Figure 2.8 illustrates is as follows, where all quantities corresponding to CFs are indicated by a star (\*). We begin with the IQHE with non interacting electrons, at  $\nu^* = n$  in a magnetic field  $B^* = \rho \Phi_0 / \nu^*$ , where  $\rho$  is the electron density. Then we attach two flux quanta to each electron, that now becomes a composite fermion. By adiabatically smearing the fluxes attached to the electrons, such that they become part of a unified magnetic field, we obtain electrons moving in an enhanced magnetic field  $B = B^* + 2\rho\Phi_0$ . This is identified as the real applied magnetic field, and as long as the energy gap closes during this transition, it implies that the filling factor takes the following values:

$$\nu = \frac{n}{2n+1} \tag{2.3.9}$$

Composite fermions form their own Landau-like levels, called  $\Lambda$  levels ( $\Lambda$ Ls), in the reduced magnetic field, and fill  $\nu^*$  of them. Thus the lowest Landau level effectively splits into these  $\Lambda$ Ls. For more details on the FQHE the reader is referred to [22] for a review of the FQHE, and to [17] for a mathematical and in-depth approach.

## 2.4 Quantum point contacts in the quantum Hall regime

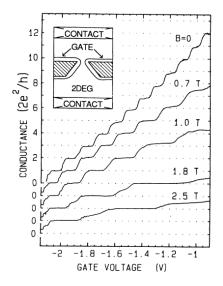

In section 2.2, we showed that at zero magnetic field, in a 1D ballistic channel, conductance is quantized in integer steps of  $2e^2/h$ . When a magnetic field is switched on, the conductance plateaus gradually become wider and flatter, as seen in Figure

2.9. When we enter the quantum Hall regime, the conductance plateaus are no longer a measure of transmitted transverse modes originating from a reservoir. The new transmission modes of the system are due to the formation of Landau levels. In the quantum Hall regime, whenever the Fermi level is parked in-between two LLs, the bulk is insulating, and the counterpropagating edge states are carrying the current across the sample. Thus, the only modes that are available are the edge states, and they must necessarily go through the QPC.

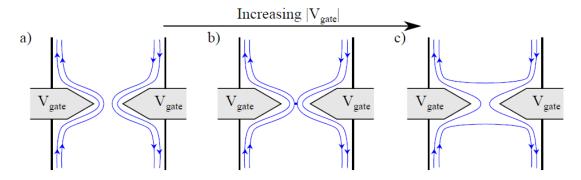

Figure 2.9: Effect of perpendicular magnetic field applied to a QPC, defined in a GaAs 2DEG. Figure adapted from [23].

At a constant magnetic field value, by making the gate voltage on the split gates of a QPC more negative, we can control the transmission and reflection of the edge channels, as is graphically shown in Figure 2.10. In Figure 2.10(a), there are two edge states ( $\nu = 2$ ) in the system, and backscattering is suppressed because of the macroscopic spatial separation of these counterpropagating states. As the split gate voltage becomes more negative, the counterpropagating edge states come closer and closer, and backscattering is introduced. Further decreasing the gate voltage results in one of the edge states to be fully transmitted, while the other is fully backscattered. This of course is the easy cartoon example for integers. Things are more complicated when fractional states are included, where compressible and incompressible regions are formed within the channel. Some examples of such experiments, of QPCs in the fractional regime include [6], [24].

Figure 2.10: (a) Bulk parked at  $\nu = 2$ , where two edge states exist. (b) As the QPC gates become more negative, backscattering is introduced, (c) One of the edge states is fully backscattered, and the other is fully transmitted. Figure adapted from [15].

## Chapter 3

## Complex Gate Geometry QPC Designs

#### **3.1** $3 \times 3$ design motivation

The main focus of the project is to find complex gate geometry QPC<sup>1</sup> designs, that allow us to control all parameters that influence their transmission properties. Furthermore, in-depth understanding and precise control of QPC confinement and QPC transmission properties, are crucial for interference and tunneling experiments within the quantum Hall regime. Ultimately, our aim is to gain a thorough understanding of how to effectively tune the potential in this specific regime of interest.

As mentioned in Chapter 1, numerous parameters can potentially influence the transport properties of a QPC. While certain factors, such as nanoscale variations in gate fabrication, are beyond our control, we wish to control the rest. As a reminder, some of those include the length and width of the channel, channel density and potential shape, as well as disorder that has an unforeseen effect on the properties of the channel.

In theory, even a simple split gate has the potential to selectively allow certain states pass through it. As a consequence, it should have the ability to locally manipulate Hall edge channels, by controlling the tunnelling probability of the counterpropagating edge channels. While this is true for numerous influential studies conducted within the research community, it is important to note that it is not always the case.

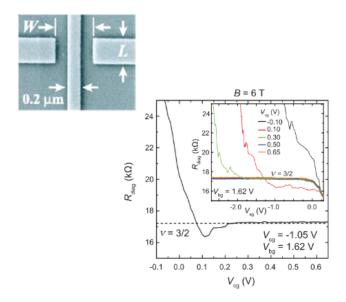

It is not guaranteed that we can always see interesting fractional states in a simple split gate QPC. The reason is that with only two gates available, there are not enough parameters that we can experimentally vary to probe the system. This observation is highlighted in this study [6], where the  $\nu = 3/2$  even denominator

<sup>&</sup>lt;sup>1</sup>In the case of length tunable QPCs we can't call them QPCs anymore, a more correct term is quantum wires or 1D ballistic channels.

state is only observed in the device featuring a center gate for controlling the QPC potential, as illustrated in Figure 3.1. Conversely, it is absent in a simple split gate device fabricated on the same material. This is just an example that underlines the critical role of the QPC potential in realizing fractional Hall states.

Figure 3.1: The top left corner shows the device, which is a split gate with an additional center gate, and the data plot shows that for positive center gate voltage, the diagonal resistance converges to the  $\nu = 3/2$  state. Figures adapted from [6].

This inherent sensitivity of fractional edge states to QPC geometry, motivates us to create more knobs through gate complexity, that allow us to control the QPC potential. In the following sections, I introduce our initial design, which is referred to as the  $3\times3$  design, and there are two generations of such devices. This thesis focuses on the investigation of the second generation of  $3\times3$  devices.

#### 3.1.1 First Generation: Single layer design

To motivate the second generation of the  $3 \times 3$  devices, we look at the results from the first generation. The device shown in Figure 3.2 was fabricated and studied by Bertram Brovang and Torbjørn Rasmussen during their master's thesis work [25], [26]. This device consists of two distinct sets of gates: the outer gates, depicted in blue, which create a wide channel when subjected to highly negative voltages, and the remaining gates forming a 3 by 3 array known as pixels. The purpose of the pixels is to divide the large square channel into a grid-like arrangement of 9 gates. The goal of their thesis work was to implement an optimization algorithm, that autonomously tuned the pixels in the best voltage configuration, with conductance quantization as the optimization criterion.

An example of the voltage configuration that the algorithm converged to is found in Figure 3.2(b). It was very counter-intuitive how the final configuration of

voltages resulted to conductance quantization. They attributed this to the connector lines of the middle pixels, causing an effect that couldn't be fully comprehended.

The first design that the current thesis is concerned with is an evolution of this single layer design, and attempts to eliminate this connector problem. We will from now on refer to this design as "the Swiss cheese design" and it is described in the following section.

Figure 3.2: (a) False color SEM of single layer 3 by 3 design. The blue gates correspond to the outer gates that are negatively biased to form a channel, and the remaining 9 gates are called pixels, (b) Results from applying optimisation algorithm, both (a) and (b) adapted from [25].

#### 3.1.2 Second Generation: Swiss cheese design

It is very hard to design a 3 by 3 grid-like array of gates in a single layer, without having the connector lines that route the middle row go through other pixels. As a result, when the middle row pixels are energized, the connectors will be as well, and this will have an effect on the operation of the rest of the pixels. For example, if a negative voltage is applied to the middle left pixel in Figure 3.2, then its connector line will block the 2DEG to the pixel below it. As a consequence, with the single layered design, the 9 pixels cannot be controlled independently as needed.

The obvious solution is to make these connectors as thin as possible, such that their effect could be minimized, but this causes practical problems in fabrication. Thinner gates below 30nm are very hard to consistently achieve in deep 2DEGs, because they tend to break <sup>2</sup>. This lowers the fabrication success yield, and