# QUANTUM PHASE TRANSITIONS IN JOSEPH-SON JUNCTION ARRAYS

Written by Andreas Skriver Olsen July 20, 2023

Supervisor Charles M. Marcus

Københavns Universitet

# Abstract

In this thesis we present a new design of semiconductor-superconductor two-dimensional Josephson junction array. The array is a square lattice of islands formed as crosses. This exposes the heterostructure material, which makes it possible to control the charge carrier density of the 2DEG by two gate potentials. The two gates allows fine tuning of competing characteristic energy scales in the array. We show that the array can be tuned into distinct regimes which significantly changes the dynamics of the array. We show that this material is a perfect platform to study an electric field driven superconductor-to-insulator quantum phase transition. We present data of the SIT in all of the characteristic regimes of the device, and we show that the prevalence of low-temperature resistance saturation is directly tunable by the gate potentials and by frustration. Furthermore we investigate the Berezinskii-Kosterlitz-Thouless (BKT) transition as a function of frustration and we show, that the the curvature of the resistance lines significantly depends of frustration. Finally we propose improvements to the design of the the frame gate layer which hopefully in the future allows for even better measurements of the SIT and BKT transitions.

## Contents

| 1        | Introduction                                                                                                                      | <b>2</b>  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1 Outline of the thesis                                                                                                         | . 2       |

| <b>2</b> | Fundamental concepts                                                                                                              | <b>2</b>  |

|          | 2.1 The 2-dimensional electron gas                                                                                                | . 2       |

|          | 2.2 Superconductivity                                                                                                             | . 2       |

|          | 2.3 Andreev reflection and the proximity effect                                                                                   | . 2       |

|          | 2.4 Josephson junction basics                                                                                                     | . 3       |

|          | 2.5 Josephson Junction Arrays                                                                                                     |           |

|          | 2.5.1 Magnetic field                                                                                                              | . 5       |

|          | 2.5.2 Temperature $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                         | . 6       |

|          | 2.6 The BKT transition                                                                                                            | . 6       |

|          | 2.7 Quantum phase transitions                                                                                                     | . 7       |

| 3        | Device fabrication and experimental setup                                                                                         | 8         |

|          | 3.1 Superconductor-semiconductor hybrid                                                                                           | . 8       |

|          | 3.2 Device fabrication                                                                                                            | . 9       |

|          | 3.2.1 Chip Wire bonding and loading                                                                                               | . 10      |

|          | 3.3 Measurement techniques                                                                                                        | . 10      |

| <b>4</b> | Results                                                                                                                           | 13        |

|          | 4.1 Preliminary measurements                                                                                                      | . 13      |

|          | 4.2 Normal state resistance                                                                                                       | . 13      |

|          | 4.3 Critical current                                                                                                              |           |

|          | 4.4 Combination gate                                                                                                              | . 16      |

|          | 4.5 Magnetic Field Scan, Frustration                                                                                              |           |

|          | 4.6 Precise determination of frustration                                                                                          |           |

|          | 4.7 The superconductor to insulator transition                                                                                    |           |

|          | 4.7.1 Device C2 $\ldots$                         |           |

|          | 4.7.2 Device $D3 \ldots \ldots$ | . 23      |

| <b>5</b> | The anomalous metallic phase                                                                                                      | <b>24</b> |

| 6        | The BKT phase transitions                                                                                                         | 28        |

|          | 6.1 Fits                                                                                                                          | . 29      |

|          | 6.1.1 Device C2                                                                                                                   |           |

|          | 6.1.2 Device D3                                                                                                                   |           |

|          | 6.2 Summary of the fits                                                                                                           |           |

| 7        | Conclusion                                                                                                                        | 37        |

## 1 Introduction

For the past 50 years, the physics of 2-dimensional superconductivity have puzzled physicist due to a complicated competing interplay between charge localization effects and the superconducting parring mechanism [38]. A huge amount of experiments on low-dimensional systems have been conducted with the goal of explain a plethora of unanswered questions: How is superconductivity destroyed by external parameters such as magnetic flux or electric fields? Can the system be driven out of superconductivity to the insulating state by introducing disorder? Do undiscovered states of matter appear in the phase transitions? Historically the majority of such experiments have been performed on thin superconducting films [10], [18]. Such films can be categorized by the type of disorder present in the system. The term "disorder" refers to random potential present in the system. The inhomogeneities of the potentials can have different length scales. Systems with variations of the random potentials on atomic scales are called uniform or homogeneous systems. If the length scale of disorder in the system is larger than the atomic length scale, the system is called granular [17]. More recently a new platform to study two-dimensional superconductivity has become popular namely the Josephson junction array. Over the last couple of decades fabrication techniques have become better which has made it possible make more complicated devices such as arrays. A huge advantage of fabricated Josephson arrays, is simply the fact that most parameters (such as physical dimensions of the superconducting islands) can be varied and chosen to desired values. Josephson junction arrays are artificially created materials hence such materials are well characterized. This is directly opposite to for instance the granular superconducting films where the Josephson coupling strength between granules are described by a distribution [3]. The Josephson junction array is a perfect system to study a plethora of physical phenomena such phase transitions (both classical and quantum) and vortex dynamics [16]. An unique feature of Josephson junction arrays is observed when a perpendicular magnetic field is applied namely frustration effects. As will be seen in section 5, due to the periodicity of arrays, the structures in the data of magnetic field sweep on arrays are much richer than for thin superconducting films.

Plenty of research has already been done on Josephson junction arrays. In this thesis however, we present measurement on a new design of the array. The device under investigation is a dual gated semiconductor-superconductor hybrid. This gives us huge amount of control of the electrostatic potential we can apply on the array which allows us to change the ratio of characteristic and competing energy scales in the system.

This device will serve as the experimental platform to study the superconductor to insulator (SIT) quantum phase transition. Due to the device being double gated, our available parameter space is very large: We have two gate potentials and a perpendicular magnetic field at our disposal. We took advantage of this by investigating the SIT at as many different combinations of the external parameters as possible. We quickly realized that multiple features in the data significantly change as a function of the external parameters. This thesis is a phenomenological description of these features.

#### 1.1 Outline of the thesis

In this thesis we present results of a series experiment aimed at gaining a deeper understanding of the SIT quantum phase transition in Josephson junction arrays. However we quickly realized that instead of having a direct transition from the superconducting to the insulating phase, we observed a " metallic" phase characterized by low-temperature resistance saturation. This will be discussed in more details in section 5. Furthermore we observed that the classical phase transition to the superconducting phase behaved differently for different magnetic field strength. This feature is discussed in section 6.

In the next section the most important theoretical concepts are introduced for the reader. In section 3 the design of the device and design improvements are presented. Furthermore the measurement setup and the general low temperature techniques we have been using are presented. In section 4 we present a sequence of results where each of the available external parameter individually are tuned and their effect on the dynamics of the array is discussed. All our SIT measurements are shown section 4. The data analysis and discussion of a BKT transition and the anomalous metallic phase are presented in section 5 and 6. Finally a conclusion of the project and of our observations are presented in section 7.

## 2 Fundamental concepts

In this chapter the theoretical background for the thesis is introduced. The review starts with a brief recap of superconductivity and the basic concepts of the Josephson junction and goes further to describe the most important physics of Josephson junction arrays.

#### 2.1 The 2-dimensional electron gas

Semiconductors are characterized by the so-called band gap energy between the valence band and the conduction band. The conduction energy of InAs is less and the conduction band energy of  $In_{0.81}Al_{0.19}As$  i.e. there is a mismatch in band gaps. Junction of semiconductors with uneven band gaps are called heterostructures. Due to the difference in conduction band energies, a quantum well is formed in the growth direction. This confinement potential "freezes out" one degree of freedom by quantizing the energy levels in the growth direction. The energy levels of the quantum wells are well described by the energy levels of the infinite square quantum well [23]

One of the most desired properties of the 2DEG, is the ability to gate the device. With a electrostatic potential we are able to tune the charge carrier density in the 2DEG. The tuneability of carrier density has been a very important tuning parameter in this project.

#### 2.2 Superconductivity

According to the theory of superconductors presented by Bardeen, Cooper and Schrieffer (BCS), below a critical temperature  $T_C$ , the fermionic ground state becomes unstable against a phonon mediated attraction between electrons near the Fermi surface with opposite momenta and spin. Such a pair is called a Cooper pair. The attractive potential between two fermions is referred to as the pairing potential. The total spin of Cooper pairs is zero which means they are bosonic particles. It turns out that the the ground state of the BCS hamiltonian is a coherent state of Cooper pairs [8]. It can be shown that the paring potential causes the energy dispersion relation of the ground state to become gapped i.e. there is a minimum energy requirement to excite the coherent state. The gap in the excitation spectrum also causes an energy gap in the density of states in the superconductor. Below the energy gap, the density of states of quasiparticle is zero.

This coherent wave function is characterized with a complex order parameter. The order parameter has a phase  $\phi$  and an amplitude which is related to the Cooper pair density:  $\sqrt{n_s}$ :

$$\Psi(r) = |\Psi(r)|e^{i\phi} \tag{1}$$

Where  $|\Psi(r)|$  is the local density of superconducting charge carriers and  $\phi(r)$  is the superconducting phase. The order parameter describes the entire condensate of Cooper pairs and is therefore a macroscopic wavefunction of the superconductor.

#### 2.3 Andreev reflection and the proximity effect

The system under investigation is a superconductor-semiconductor hybrid. Therefore the normalsuperconducting interface has to be taken into account. It turns out that a special reflection process occurs, the so-called Andreev reflection or retroreflection. Consider an electron with energy less than the superconducting gap. Due to the gap, no single electron states are available hence no transmission through the interface is allowed. Furthermore, it cannot be scattered normally because no scattering potential is present at the interface. Instead, a Cooper pair can be created in the superconductor by taking an additional electron near the Fermi surface of the normal material. This vacancy in the normal material is referred to as a "hole". The incoming electron is retroreflected as a hole with opposite spin and momentum at the N-S interface. This effectively transfers two electrons from the normal material to the superconductor in the form of a Cooper pair. The model described above can be extended to include a non-zero amplitude of normal scattering by adding a potential at the interface. The so-called BKT model introduces a delta function potential at the NS interface [30].

The process described above resulted in adding a Cooper pair to the superconductor condensate. A Cooper pair from the the condensate and leak into the normal material and diffuse a short distance. Effectively the pairing potential from the superconductor does not abruptly stop at the NS interface can leak into the normal material with decaying amplitude. The characteristic length scale of this decay is the coherence length of the Cooper pairs [26].

#### 2.4 Josephson junction basics

A Josephson junction consists of two superconducting leads separated by a layer of non-superconducting, the so-called weak link. Examples of Josephson junction are the superconductor-insulator-superconductor (SIS) junction where the weak link is a insulating material or a superconductor-normal-superconductor where the weak link is a metal (SNS) (More types of junctions exists [31]). It was discovered by Brian Josephson that a current can flow between the superconducting leads even without a potential difference. This phenomenon is hence called the Josephson effect. It originates from the coherent tunneling of Cooper pairs between the superconducting leads.

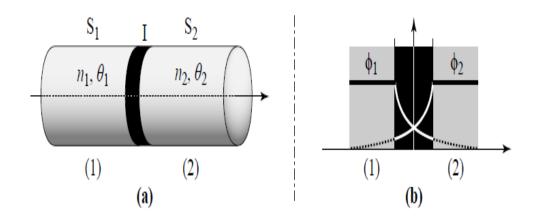

Figure 1: **a**) A schematic of a SIS junction [30]. Each superconducting lead is characterized by the macroscopic wavefunction. **b**) The overlap over wavefunctions leads to non-zero probability of Cooper pair tunneling.

A schematic of a SIS junction is shown in figure 1. Each superconducting lead is described by the wavefunction in equation 1. The wavefunction of the right lead can extend into the left lead and vice versa. This causes a non-zero probability of Cooper pair tunneling between the leads. Josephson derived that the current flowing between the two leads is given as:

$$I = I_c \cdot \sin(\phi_2 - \phi_1) \tag{2}$$

Where  $I_c$  is critical current which is the the maximal dissipationless current sustained by the junction. It is not a potential difference but a phase difference that drives the supercurrent. Even though the tunneling current is dissipationless, there is still energy stored in the junction. The Josephson junction in figure 1 can be thought of as a molecule with a binding energy resulting from the wave function overlap. This "binding" energy of the Josephson junction is the so-called Josephson coupling energy. The Josephson energy represents the junction coupling strength. It plays an extremely important role in the measurements shown in this thesis [32].

When an external magnetic fields is applied it interacts with the Josephson junctions via. its vector potential. It is well known from introductory electromagnetism, that there exists no unique vector potential for a given magnetic field. In order to select a specific vector potential to work with for a given magnetic field, one has to choose a specific gauge. The superconducting phase and the vector potential obeys a set of gauge transformations. All physical quantities have to be independent of the gauge choice . A gauge invariant phase difference between two superconducting islands is therefore introduced:

$$\gamma_{ij} = \phi_i - \phi_j - \frac{2\pi}{\Phi_0} \cdot \int_i^j \vec{A} \cdot d\vec{r}$$

(3)

If a constant potential difference applied across the junction, it can be shown that the phase difference grows linearly as a function of time:

$$\frac{d\Phi}{dt} = \frac{2\pi}{\Phi_0} V \tag{4}$$

Where  $\Phi_0 = \frac{h}{2e}$  is the flux quantum. It is seen that time evolution of the phase difference causes dissipation in the junction since it. This is a very important equation is used to explain the resistive behavior of arrays.

So far only the dissipationless supercurrent has been accounted for (eq. 2). But the Josephson junction consists of two separates pieces of metal. A capacitive current is given as  $I = C \cdot \frac{dV}{dt}$ . Inserting equation 4 gives the following expression:

$$I_C = \frac{\hbar C}{2e} \frac{d^2 \phi}{dt^2} \tag{5}$$

#### 2.5 Josephson Junction Arrays

Understanding the basics of single Josephson junction, one can go further to derive equations that describe the dynamics of an array of Josephson junctions. A Josephson junction array is made up of an ordered pattern of superconducting islands. Adjacent islands are weakly coupled by Josephson interactions. The lattice pattern investigated in this thesis is a square array. Each islands are weakly coupled to four adjacent islands.

The hamiltonian of the array is constructed simply by summing the junction potential energies (The capacitive and Josephson binding energy) for all junctions in the array. The following Hamiltonian is obtained:

$$H = \frac{1}{2} \sum_{\langle ij \rangle} C\left(\frac{\hbar}{2e}\right)^2 \left[\frac{d}{dt}(\gamma_{ij})\right]^2 - J \sum_{\langle ij \rangle} \cos(\gamma_{ij}) \tag{6}$$

Where the summation is over nearest neighbors. The first term is the energy required to add additional charge to an island and the second term is the Josephson tunneling energy between adjacent islands. This model is usually referred to as the quantum phase model (QPM). The reason for this is the fact that the superconducting amplitude on each island is not included. This hamiltonian only takes the superconducting phase into consideration. It is seen in the Hamiltonian in equation 6 that there is a competition between the Cooper pair tunneling term and the charging energy term. These two characteristic energies determine the dynamics of the array namely the Josephson energy  $E_J$  and the charging energy  $E_C$ . The former energy scale determines the strength of the Josephson coupling and the later determines the energy cost of adding additional charge to single island. The  $\frac{E_J}{E_C}$  ratio is a important parameter which separates the array into two regimes: A classic and quantum array. Arrays are classified as being classical when  $E_C \ll E_J$ . In the classical limit a global phase coherence can be established and the array is superconducting. In the opposite limit  $E_J \ll E_C$  the system becomes a Mott insulator due the large charging energy [16]. This results in a localization of Cooper pair on each island. It can be showed that the Hamiltonian of classical arrays is isomorphic to the two-dimensional XY-model. The fact that Josephson arrays are believed to be a physical realization of the XY-model has made it a heavily investigated topic, both experimentally and theoretically.

In the classical limit, the Josephson energy is dominating. Hence the charging energy term in the Hamiltonian can be ignored. The hamiltonian in equation 6 is reduced to the following:

$$H = -J \sum_{\langle ij \rangle} \cos(\phi_i - \phi_j - \frac{2\pi}{\Phi_0} \cdot \int_i^j \vec{A} \cdot d\vec{r})$$

<sup>(7)</sup>

This Hamiltonian has the same for as the so-called XY-model (the cosine can be written as a dot product of two two-dimensional unit vectors  $S_i \cdot S_j$ ). The Hamiltonian in equation 7 is used to introduces the very important concept of vortices.

Every island in the array is characterized by its superconducting phase. It is seen in expression of the superconducting order parameter 1 that the phase is defined modulo  $2\pi$ . Summing the phase difference across junctions in any closed path there must give  $2\pi n$  with n begin an integer. Consider the hamiltonian 7 without an applied magnetic field (A = 0). It is clearly seen that the energy of the array is minimized by making the superconducting phase equal on all the islands. This phase configuration simultaneously satisfy the following condition:

$$\sum_{closedpath} \cos(\phi_i - \phi_j) = 2\pi n \tag{8}$$

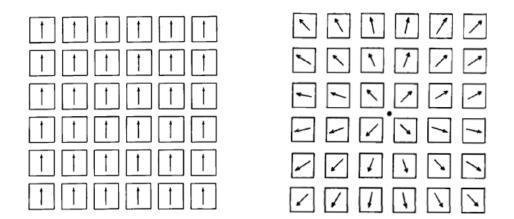

For n = 0. The ground state configuration of the phases is shown in figure 2 All the phases are equal. We now search for phase configuration that satisfy 8 for n = 1. This phase configuration is shown in figure 2. A vortex (antivortex) is an excitation in the phase configuration such that the sum of all phase difference along a closed loop is  $2\pi$  ( $-2\pi$ ) [21]. The vortex core is not necessarily located in the plaquette center as shown in figure 2. Phase configurations with other vortex core locations exists. The energy of every configuration is different. The energy differences between every configuration represent a potential landscape in which the vortices are moving. Stationary vortices are located in local minima in this potential. It is seen in equation 4 that a frozen vortex does not generate a voltage across the array. However vortices can be depinned by a biasing current or by thermal fluctuations. Free vortices in the array causes a voltage to appear.

Figure 2: a) The ground state phase configuration. Every phase is aligned. b) The ground state phase configuration with a single vortex injected into the array. The phases have rearranged such that they cancel the additional phase term from the vector potential [31].

#### 2.5.1 Magnetic field

The magnetic field introduces an additional phase difference  $A_{ij}$  across the junctions. The sum of  $A_{ij}$  around the four junctions in a plaquette is related to the applied flux though the plaquette [21]:

$$\sum_{plaquette} A_{ij} = \frac{2\pi BS}{\Phi_0} = 2\pi f \tag{9}$$

Where B is the applied flux and S is the plaquette area. f is referred to as the frustration parameter and is defined as the applied flux divided by the flux quantum. Consider the scenario of applying a single flux quantum across the entire array. The sum of all phase difference for for all the junction in the array is therefore  $2\pi$ . The ground state of the energy is no longer the uniformly distributed configuration shown in figure 2. However it is seen in the Hamiltonian that the energy of the system can be reduced if the phase difference adjust to cancel the phase gained from the vector potential. This configuration is shown in figure 2.

When a magnetic field is applied, the field penetrates the Josephson junction array by creating vortices similar to a type-II superconductor [28]. The major difference between JJa's and homogeneous type-II superconductors is the spatial configurations of vortices. In type-II superconductors the vortex lattice is triangular (The so-called Abrikosov lattice). The vortex lattice in Josephson arrays are more complicated since the spatial configuration of the vortex lattice in JJa's depends on the frustration parameter f [36]. Vortex lattices in JJa's is discussed in later sections.

#### 2.5.2 Temperature

At non-zero temperature, vortices can be injected into the array if the thermal energy fluctuations are large enough. It can be shown that the energy cost of a single vortex excitation of the ground state phase configuration is the following (This is formally done by Taylor expanding the cosine in equation 7 and take the continuum limit. The field configuration which corresponds to a minima in the Hamiltonian is the vortex solution [33]):

$$E_{vortex} - E_0 \propto \pi E_J \ln(\frac{L}{a}) \tag{10}$$

Where a is the distance between islands and L is the width of the entire array. For large arrays, the energy cost of adding a single vortex is enormous. The probability of observing a single vortex in the array can be estimated by using the change in free energy by injecting a single vortex in the Boltzmann distribution:

$$P \propto \left(\frac{L}{a}\right)^{2 - \frac{\pi E_J}{k_B T}} \tag{11}$$

For large arrays the probability is virtually zero until the exponent in equation 11 becomes zero at which the probability immediately increases to unity. The temperature at which this happens is defined as the Berezinskii-Kosterlitz-Thouless (BKT) temperature:

$$T_{KT} = \frac{\pi E_J}{2k_B} \tag{12}$$

This is the lowest temperature at which free vortices can be found in infinitely large arrays. At temperatures below the BKT temperature, thermal fluctuations do not generate free vortices due to the large energy cost. However, it can be shown that the energy cost of injecting a bound pair of two vortices with opposite sign is significantly lower than injecting a single free vortex:

$$E_{Pair} = 2\pi E_J \ln(\frac{r}{a}) \tag{13}$$

Where r is the distance between the vortex cores. If the distance between the vortex pair is less than the system width, the energy is significantly lower a single thermally injected vortex. As the temperature is increased from below, more and larger vortex pairs are generated. At the BKT temperature, thermal fluctuations become large enough to break the largest vortex pairs and create free vortices.

#### 2.6 The BKT transition

Above the BKT temperature free vortices are present in the array which causes the array to be resistive. Below the BKT temperatures, all vortices are bound and the array is superconducting. At the BKT temperature a phase transition occurs between a resistive phase and the superconducting phase. Continuous phase transitions are characterized by diverging correlation length at the critical point [35]. It can be shown that the vortex correlation length for the XY-model is the following:

$$\xi = a e^{\left(\frac{b}{T - T_{BKT}}\right)^{\frac{1}{2}}} \tag{14}$$

For temperatures  $T > T_{BKT}$ . a and b are constants. The correlation length determines the average distance between free unbound vortices. At the BKT temperature, the correlation length is infinite indicating that there are no free vortices in the array.

The correlation length is used to derive an very important expression for the array resistance as a function of temperature. The resistance of the array is proportional to the density of free vortices which is proportional to 1 over the average distance between free vortices squared i.e.  $\xi^{-2}$ .

$$R(T) = ae^{-b\left(\frac{E_J}{T - T_{BKT}}\right)^{\frac{1}{2}}}$$

(15)

The function is defined for temperatures above the BKT temperature. For  $T > T_{BKT}$  and R(T) = 0 for  $T < T_{BKT}$ . This expression is extremely important and is extensively in the data analysis section. Equation 15 has been derived from the Hamiltonian in equation 7. So far it has been assumed that the coupling strength (i.e. the Josephson energy) remains constant as a function of temperature. Therefore the temperature in equation 15 is can be replaced with a reduced temperature (defined as  $\frac{T}{E_T}$ ):

$$\tilde{T} = \frac{2\pi k_B T}{\Phi_0 i_c(T)} \tag{16}$$

A more detailed discussion about the BKT phase transition and the temperature dependence of the array resistance is presented in a later section.

#### 2.7 Quantum phase transitions

For classical phase transitions the system is driven through its critical point by the temperature. At the critical point the ground state fundamentally changes which often can be seen as diverging characteristic length scales. This is seen in the vortex correlation leg nth (eq. 14). The driving parameter of a quantum phase transition is however not the temperature. The SIT in Josephson junction array is an example of a quantum phase transition. A quantum phase transition can occur if the temperature is low enough such that quantum fluctuations are dominant. Quantum fluctuations is the driving the system through it critical point. If thermal fluctuations are much larger than quantum fluctuations, then the phase transition is purely classical.

Quantum fluctuations originates from the Heisenberg uncertainty principle and are present even at absolute zero. The Heisenberg uncertainty at play in Josephson junction arrays is the following:

$$[\phi_i, Q_j] \propto \delta_{ij} \tag{17}$$

The phase of the order parameter and charge are conjugate variables. Superconductivity on each island is governed by the local pair amplitude, but global superconductivity of the array is only achieved when a phase coherent path through the array is established [37]. Strong fluctuations in the phase prevents the establishment of phase coherence across the array. Global superconductivity remains as long as the following correlator approaches a non-zero value for  $\mathbf{r} \to \infty$ .

$$G(\mathbf{r}) = \langle \psi(\mathbf{r})\psi(0) \rangle \tag{18}$$

Enhancing the quantum fluctuations of the phase can lead to suppression of superconductivity. In our experiments, this is achieved by increasing the frame gate voltage. This increases the  $E_C/E_J$  ratio which localizes charge. This mechanism of destroying superconductivity due to phase fluctuations is called "the Bosonic scenario". It is seen in the 18 that it is possible to suppress superconductivity if the modulus of the order parameter vanishes. This is the "fermionic scenario". Instead of localization of Cooper, it is electronic excitation that is responsible for the suppression of superconductivity [29].

## 3 Device fabrication and experimental setup

The design of the device and the electron transport measurement setup are presented in this section. Common low temperature techniques are discussed as well as the most important principles such as the lock in amplifier and 4-terminal measurement.

#### 3.1 Superconductor-semiconductor hybrid

The fabrication and designs of the devices have not been a part of this master project. When I joined the project, the chip had already been fabricated, bonded and loaded in the dilution refrigerator. The main focus of this thesis is the electronic transport properties of the Josephson junction arrays. This being said, during the measurements we very quickly found flaws in the design of the arrays and we have new design proposals. This will be be discussed in later sections.

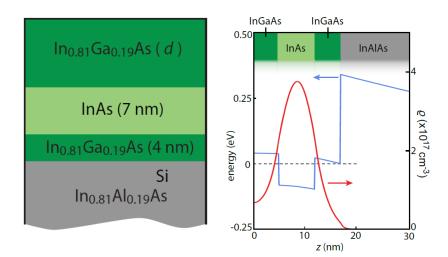

The device under investigation is a two-dimensional superconductor-semiconductor hybrid heterostructure. The wafer was grown by the Manfra group at Purdue university and the fabrication of the device was done by Sangeeth Kallatt in the clean room of center of quantum devices at University of Copenhagen. The heterostructure was grown on an insulating InP substrate. The layer structure of the quantum well (the so-called stack) and the electron wave function are shown in figure 3. The electronic properties the quantum well has previously been studied by Shabani et al. [25]. They studied the properties of the near surface quantum well as a function of varying the surface layer thickness (d) and calculated the electron wavefunction of the 2DEG electron carriers. The thickness of the heterostructure surface layer the devices in this project is 7nm.

Figure 3: Left to right: **a**) The stack and quantum well of the devices under investigation. **b**) The electron wave function in quantum well [25].

On top of the stack, an 5nm aluminum layer has been grown. The aluminum layer have been grown using molecular beam epitaxy. This method allows the growth of highly homogeneous layers and very clean interfaces between the heterostructure and the aluminum. A clean interface is important to enhance the proximity coupling. When the device is cooled to temperatures below 1.8K, the aluminum becomes superconducting. Due to the proximity effect, the superconducting pairing potential decays into the quantum well.

Enhancing the proximity coupling comes with a cost. In order to improve the proximity coupling between the superconducting aluminum layer and the 2DEG, the charge carriers must be near the surface which decreases the carrier mobility. The electron mobility of the heterostructure was also measured by Shabani et al. The electron mobility is not very high since the quantum well is close to the surface which causes the surface scattering rate to be high. In order increase the proximity coupling to the 2DEG, the electron wavefunction must reach the aluminum layer. It is seen in figure 3 b) that the electron wavefunction does extend into the surface.

#### 3.2 Device fabrication

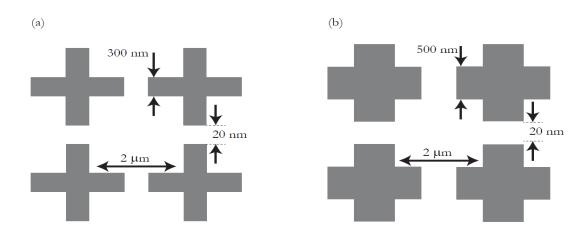

The entire chip consists of 12 Hall bars with varying plaquette areas, junction widths and lengths. The array is made of aluminum islands shaped as a cross. The array consists of junctions placed in a regular square lattice. In this project we have been conducting experiments of two different devices. An overview of the two arrays under investigation is shown in figure 4.

Figure 4: From left to right: a) The only difference between the two arrays is the width of the junctions. This device is referred to as C2. b) The width of the junction is increased to 500nm. This device is referred to as D3. The plaquette area is  $2x2\mu m^2$  for both devices.

The following section is a brief summary of the fabrication procedure. The initial step of the chip preparation is the mesa patterning. The chip is spin coated with resist and the mesa pattern is defined using e-beam lithography. All mesas are shaped as Hall bars. The etching of mesas consist of multiple steps. The aluminum layer must first be removed which is done using aluminum etchant. A separate etchant is used for the mesa etch (solution of water, citric acid, phosphoric acid and hydrogen peroxide). It is important to make sure the mesa etch is deep enough to the insulating area of the wafer to prevent leaking conduction paths between the mesas. Afterwards the resist used for mesa patterning is removed. The next step is the fabrication of the aluminum islands. Between every layer, the chip is always spin coated with resist and e-beam lithography is used for the patterning of the array itself. Removing parts of the aluminum layer makes it possible to gate the device since the electric field lines form the gate can no longer be screened by the aluminum.

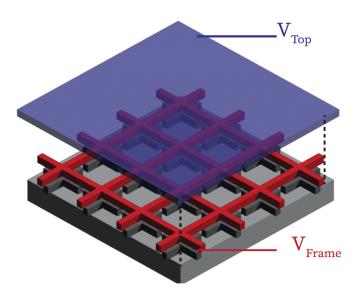

The novelty of our experiment is the fact that the device is dual gated. A schematic of the Josephson junction array is shown in figure 5. The two gate layers are made of Gold and titanium (Au/Ti). To prevent currents through the gate layer to the device and to ensure a purely capacitive coupling, a dielectric layer is deposited. The dielectric medium between the gate layer and the aluminum surface consists of a 40 nm aluminum oxide layer. The dielectric is deposited using atomic layer deposition (ALD). The gate layers are deposited using e-bream evaporation. The sequence at which the two gates layers are deposited is very important. The frame gate layer must be placed underneath the top gate layer. The electric field from the top gate is screened by the field lines from the frame gate. This configuration of the two gates makes it possible to tune the Josephson energy with the frame gate only and make it independent of the top gate voltage.

Figure 5: The general design of every device on the chip. The array consists of the aluminum island formed as a cross. The first gate layer is frame gate which controls the electrostatic potential across the junctions. The final layer is the top gate which applies a potential on the exposed 2DEG.

#### 3.2.1 Chip Wire bonding and loading

After fabrication, the chip is glued to a sample holder on a daughterboard. The chip must be be electrically connected to the daughterboard. This is done by wire bonding the leads of the device to bond pads located on the edges of the daughterboard. The wire bonding is achieved using special bonding equipment. The material used for the bonding is gold. Afterwards the daughterboard is connected to a motherboard which is placed inside a puck. The puck is loaded into the cryostat from the bottom using a special designed loader which has its own vacuum chamber. The puck is placed in this chamber. The vacuum chamber of the loader is then vacated using a scroll and turbo pump. When the pressure in the loader vacuum chamber is comparable to the pressure of cryostat vacuum can, the chamber is opened and the puck is screwed onto a cold finger. This brings the sample in thermal contact with the mixing chamber plate. Coaxial cables are connected to the break out box and are used to connect measurement instruments to the setup.

#### 3.3 Measurement techniques

In order to study quantum mechanical effects, the temperature of the system under investigation has to be low. This is due to the large difference in energy scale between quantum and thermal fluctuations at high temperatures. The energy scale for quantum mechanical phenomena much lower than the energy scale of thermal energy. The thermal energy is of order  $k_BT$ , hence the temperature has to be significantly lower than room temperature. We achieve low temperatures using a <sup>3</sup>He/<sup>4</sup>He dilution refrigerator. We use a Oxford Instruments Triton 400 cryostat which is a pulse tube dry refrigerator. The base temperature is 15mK.

All of our experiments have been conducted using two methods of biasing: Voltage and current bias. Voltage bias was used to measure zero bias differential resistance of the device whereas current biasing was used to measure the critical current of the device. Voltage biasing consists of applying a voltage the source ohmic of the device. AC and DC voltages are combined through a voltage divider. The voltage divider is used to down scale the voltage generated by the connected voltages sources. This allows for more fine tuning of the voltage and can give higher resolution than what is possible with the voltage source. The AC voltage is divided by 10000 and the DC voltage is divided by 1000. The DC voltage was generated using either Yokogawa or a Qdevil qdac. The current going out of the

device was preamplified using an IV-converter (Basel Precision Instruments). The preamplification gain was set to 1e8. The longitudinal voltage was preamplified by a factor 1000 using a home-built voltage preamplifier.

A 4-terminal setup was used to measure the voltage drop across the sample and between ohmics on the sides of the Hall bar. The device under investigation is superconducting. Therefore it is very important to be able to measure very small resistances. The principle behind a 4-terminal measurement is to separate the probing circuit and the driving circuit such that no current is running in the sensing circuit. The impedance of a voltmeter is very high. Therefore no current is running through the sensing circuit hence there is no voltage drop across the wire contacts. The voltage drop across the drive leads are not seen by the sensing leads. Unfortunately the lowest resistance we can measure in the setup is  $3\Omega$  even when the device should be superconducting. We do not know the reason for this.

A slightly different measurement setup was used when current biasing the sample. The voltage was not applied directly to the ohmic. Instead a  $10M\omega$  resistor was put in series for the DC voltage and a  $1M\omega$  resistor of the AC voltage. This ensures that the entire voltage drops across the resistor. The current through the device is therefore approximately constant. When current biasing the sample, one has to be very careful to make sure, that the resistance of the sample itself is lower than the  $10M\Omega$  resistor on the DC line. If the resistance of the device becomes of similar value as the resistor, a significant voltage is dropped across the sample which may damage to the sample.

The magnetic field has been produced by a superconducting (6, 1, 1) vector magnet. We have only used very small magnetic field strength. We used a Keithly Source meter to fine tune the magnetic field.

Typical low-temperature experiments consists of measuring currents and voltages with very low amplitudes. Such signals can easily be buried in noise. Lock-in amplifiers are used to drastically enhance the noise to signal ration. Lock-in amplifiers can detect AC signals with very small amplitudes. The principle of lock-in amplifiers is called phase-sensitive detection [1]. Noise components of the detected signal with frequency different from the lock-in reference frequency, are significantly attenuated. The lock-in generates an internal reference sine signal with a fixed frequency  $\Omega_{ref}$ , phase  $\theta_{ref}$ and amplitude  $V_{ref}$ . This reference signal is used to excite the experiment. This causes the response of the system to be frequency modulated with the reference frequency  $\theta_{ref}$ . The expected output signal of the experiment is hence a sine wave with the same frequency  $\theta_{ref}$  plus additional noise signals at frequencies different from the reference frequency. The phase-sensitive detection (PSD) consists of mixing the reference signal and the output signal. Mathematically this operation generates the product of the two cosine waves. The resulting out of the PSD is the following:

$$V_{PSD} = \frac{1}{2} V_{sig} V_{ref} \cos((\omega_{sig} - \omega_{ref}) + \theta_{sig} - \theta_{ref}) + \frac{1}{2} V_{sig} V_{ref} \cos((\omega_{sig} + \omega_{ref}) + \theta_{sig} + \theta_{ref})$$

(19)

The PSD generates two AC signals. For signal frequencies  $\omega_{sig} \approx \omega_{ref}$ , the first cosine become a DC signal and the second cosine becomes a high frequency AC signal. A low pass filter is used to remove the high frequency part hence the resulting out after the PSD is a DC signal. Noise components with frequencies far away from the reference signal is attenuated by the low pass filter since both cosines in eq. 19 become high frequency signals. The PSD output for noise components with frequencies close to the reference frequency is low frequency AC signal. The low pass filter time-constant determines the attenuation of such signals. The lock-in amplifier determines the phase difference  $\theta sig - \theta_{ref}$  by adding a second PSD with a 90 degree phase shift of the reference signal.

All transport measurements have been performed using a combination of multiple Stanford research system lock-in model SR860 and SR830. The voltage drop across the sample and the current running through the device are both measured with lockin amplifiers. Dividing the voltage by the current (remember to include the preamplification factors), one obtains the differential resistance i.e. the slope of the IV characteristic of the array. Implicitly we are assuming that the IV-curve of the array is anti-symmetric around zero bias and that the slope around zero bias is approximated well as a linear function. In that case the differential resistance and the absolute resistance of the device is approximately identical. The amplitude of the lockin excitations determines the precision of the derivative of the IV-curve. A large amplitude might generate less noisy signals, but sacrifices resolution. We used a  $5\mu$ V AC excitation for all our SIT measurement.

The lockin excitation frequency is set to a rather low value of 3.14 Hz. The reason for this is due to the C2 device behaving as a low pass filter. The amplitude of the current was significantly attenuated when the lockin frequency was increased to higher values. The low pass filter characteristic was not significant in device D3 so the lockin frequency was set to 27.3 Hz.

## 4 Results

In this chapter all the conducted measurements on the chip are presented. The entire available parameter space is explored and the effect on the device of each of the tuning parameters is analyzed.

#### 4.1 Preliminary measurements

Before actual experiments of each device on the chip can start, it is necessary to investigate which devices are working as intended and which have defects from the fabrication. Fabrication of nanos-tructures is difficult and complicated, and errors in the fabrication process can easily happen. The quality of each device are systematically checked by doing a handful of simple measurements.

The preliminary measurement consists of checking for leaking conduction pathways. The first measurements were gate leakage test. This measurement is conducted to find faulty gates and to map out the available gate space. The gate layers and the array are separated by a aluminumoxide dielectric layer. Bad ALD growth of the dielectric layer may cause a leaking current from the gate plates to the array. The test consists of sweeping the gate voltage while measuring the current. The quality of the probes must also be checked. A significant problem that often arises is the probe pinching off. The gate voltages are swept while the phase of the voltage probes are measured. Probe pinch-off is observed as a 90 degree phase shift.

The preliminary measurements on the chip has reduced the available number of devices from 12 to only two. The majority of the electron transport measurements have been done on device C2 and D3. The different geometry of these two devices makes it possible to directly compare the data of the two devices and investigate the effect of changing the dimensions of array parameters such as junction width and plaquette area. Furthermore it allows us to check the validity of unexpected features appearing in the device. If the same feature appear in multiple devices, it is easier to argue that new physics is going on.

#### 4.2 Normal state resistance

The available parameter space for our device is vast. It is important to investigate the effect each of our tuning parameters have on the device. This section focuses on the effects of the top and frame gates. The two gates allows us to independently adjust the electrostatic potentials in the junctions and the plaquettes and give enormous tuneability of the charging and Josephson energies.

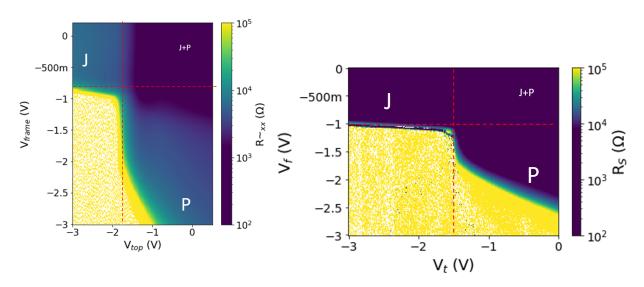

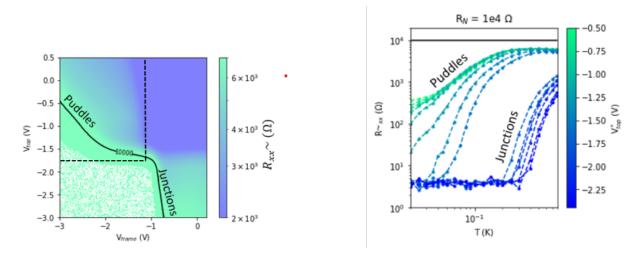

The first experiment on each device is measuring the normal state resistance (temperature is 2K) as a function gate voltages. The gate maps of device C2 and D3 are shown in figure 6. The maps have been obtained by setting the frame gate voltage sweep as the inner loop in qcodes and the top gate voltage sweep as the outer loop. Very early on in the project it was observed, that sweeping the top gate voltage causes hysteretic behavior. This hysteretic behavior is much less pronounced when sweeping the frame gate. The device is very large so probably a huge amount of metastable states that are very close in energy exists. Every time the top gate potential is swept, the array my settle in slightly different ground states.

The behavior of the array significantly depends on the gate potentials. The combined effect of the two gate potentials allow us to tune the array into different regimes each of which have unique behavior.

The frame gate potential allows us to tune the conductance through the junctions and hence is directly related to the Josephson energy. The driving parameter of the quantum phase transition is the ratio of the two the junction energy and the charging energy of the array. Hence the frame gate potential is our main driving parameter in the quantum phase transition from the superconducting phase to the insulating phase.

Figure 6: The figures shows the resistance of the device as a function top-gate and frame gate-voltages. The maps was measured at 2 K. The map on the left/right is the gate map of device C2/D3.

The top gate controls the fermion density in the plaquettes of the unit cell in the array. The exact effect of the fermion density in the plaquettes on the quantum phase transition is unclear, but it has been suggested that it can be modeled as reservoir of low lying fermionic excitations which acts as a dissipative bath for the superconducting order parameter [2].

The first noticeably feature is the areas of decreasing resistance in the gate scan of device C2 shown in figure 6. There are vertical and horizontal "band" of less resistance which is present at top gate voltage -0.75V and frame gate voltage -1.7V. We suggest this feature might be due to a mobility peak in the 2DEG. The mobility peak indicates that interface scattering can be suppressed. This is consistent with the fact that the quantum well is close to the aluminum interface. Shabani et al. were able to increase the mobility of the 2DEG carriers by increasing the thickness of the quantum well surface layer. This burrows the quantum well further from the surface and hence decreases surface scattering. We are able to push the quantum well further away from the surface by applying an electric potential.

The main features in the both gate maps is the clear separation of gate space into different areas. There are four different regimes in the device. The first is the "puddle regime" which occurs when the top gate is slightly energized (voltage near zero) and the frame gate is highly energized (large negative voltage). The area in gate space is shown with the letter P in figure 6. In the puddle regime the fermion density in the plaquettes is large while the highly energized frame gate significantly decreases the conductance through the junctions. In this regime the transport of electrons goes around the junctions through the plaquettes.

The second regimes is the "junction regime". The area in gate space is marked with a J. The top gate is highly energized which depletes the plaquette density and makes conductance through the puddles very small. The frame gate voltage is near zero which makes the Josephson junction energy very high. In this regime the junctions are fully open and the majority of carrier transport happens through the junctions.

The third regime is a complicated area where both gates are slightly energized, but neither are set to an extreme value. It is shown as a J+P marker in the gate space map. This is a very complicated regime so we decided not to investigate this regime.

The last regime is the insulating area. In the yellow area, both the gates are highly energized. Conduction paths through the plaquettes and through the junctions are all closed.

A key feature in the gate-gate maps for both devices is the presence of two different slops of the insulating area. The vertical red dashed line indicates the first slope. The general shape of the yellow

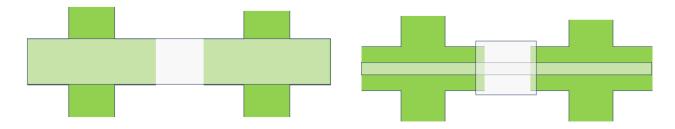

insulating area is a sharp corner followed by another area with a less steep slope. The corner occurs at the point in gate space where the junctions are fully closed and the puddle conductance channels are just about to open. Starting from the intersection of the two red dashed lines, going more negative on the frame gate doesn't change the array resistance since the junctions already are closed off and the majority of conductance occurs through the plaquettes. This is true until the second slope occurs. At this point the frame gate significantly increases the resistance. We believe this feature can be prevented by changing the frame gate design. The current and a newly proposed design are showed in figure 7.

Figure 7: From left to right. a): The current design of the frame gate. The width of the frame gates is the same as the junction width. b) The new design of the frame gate. The width has been reduced except for the area between the junctions.

In the current design of the arrays, the frame gate width is the same as the width of the underlying aluminum layers. Slight misalignment of the frame gate layer makes it possible for the electric field lines of the frame gate to reach the heterostructure since they are no longer screened by the aluminum layer. At high frame gate voltages, this causes the frame gate to effectively pinches off the both the junction conductance and the puddle conductance. This is the reason for the second slope in the gate-gate maps. We therefore propose to make the changes shown in figure 7. The width of the frame gate layer has been reduced such that it no longer matches the width of the underlying aluminum layer. The width of the frame gate above the junction itself remains the same. The new design significantly reduces the possibility of puddles conduction pinch-off by the frame gate. Devices with these design changes have already been fabricated, and measurements have been conducted by Luca Felix Banszerus. Gate-gate maps of the devices have been obtained and the second slop has indeed disappeared.

#### 4.3 Critical current

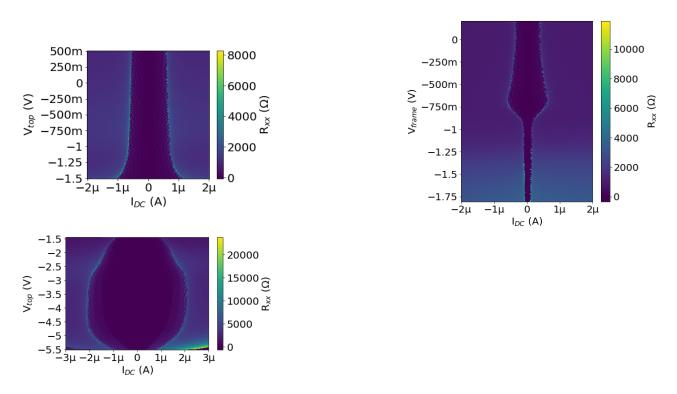

The gate maps reveal the array behavior when the aluminum is normal (at 2K). At base temperature (15mK) the different regimes are characterized by their critical current. The measurement is conducted by applying a DC biasing current to the source probe. If the applied current exceeds the critical current of the array, a voltage drops across the sample, since part of the current becomes dissipative. The critical current of device C2 was measured at different gate space configurations at base temperature (15mK).

The differential resistance maps are shown in figure 8. The two plots on the left side show the differential resistance of the array as a function of sweeping the top gate voltage. The frame gate is held constant at  $V_f = -0.6$ V i.e. the junctions are open and the top gate is swept from 0.5V to -5.5V. This gate sweep can be visualized in the gate map of device C2 (Figure 6) as a horizontal line at  $V_f = -0.6V$  from the J+P regime to the junction regime. It is seen that the differential resistance is largely independent of the top gate potential in the range 0.5V to -1.25V. Increasing the top gate voltage in the interval between -1.25V and -5.0V drastically increases the critical current of the array. The top gate voltage controls the fermion density in the plaquettes. We suggests that the dramatic increase in critical current is rooted in the inverse proximity effect. The inverse proximity effect is a suppression of the superconducting gap near the surface between a superconductor and a reservoir of fermionic excitations. When the top gate voltage becomes very large, the fermion density in the puddles become very low. This reduces the inverse proximity effect, which causes the critical

Figure 8: The critical current measurements have been taken at 15mK.

current to increase. The critical current significantly decreases at top gate voltages above -5.0V. This is probably due to an unintended cross capacitance between the top gate and the 2DEG underneath the frame gate. At such large voltages, the electric field lines from the top gate effectively pinches off the conductance through the junctions.

The figure on the right side shows the differential resistance as a function of the frame gate at fixed top gate voltage  $V_T=0.5$ V. The line cut in the gate map is the vertical line at  $V_T=0.5$ V going from the J+P region to the puddles region. The critical current is significantly smaller due to the large fermion density in the plaquettes. In the frame gate interval  $V_f = 0V$  to -0.75V the critical current slightly increases. At higher frame gate voltages, the junctions are closed off and the critical current almost reaches zero.

The critical current scans strongly suggests, that the plaquette fermion density significantly suppresses superconductivity of the array. The magnitude of the critical current in the puddles and junction regimes are very different. The magnitude of a supercurrent going through the plaquettes is significantly reduced due to the inverse proximity effect.

#### 4.4 Combination gate

Knowing we have multiple regimes in the array, we would like to sweep along a path in gate space that connects the two regimes, and investigate the features of the resistance lines along this path as a function of temperature. We were inspired by the Ambegaokar relation which makes a connection between the normal state resistance of a Josephson junctions and its Josephson energy. Hence the chosen paths in gate space were iso-resistance lines. Contour lines were found in the gate map shown in figure 6. The frame and top gate voltage combinations along the contour line was coded into a single sweeping parameter in qcodes. This "combination" gate map sweep was performed at multiple temperatures in the interval 20mK to 1.9K. The resistance lines as a function of temperature along the contour line at  $10k\Omega$  is shown in figure 9. The key feature is the fact that the resistance lines are clearly divided into two regions. In the junction regime the resistance lines become superconducting at much higher temperatures than the the lines in the puddle regime. In fact, the resistance lines in the puddle regime do not become superconducting at all. The separation of resistance lines in the two regimes reaffirms the fact that the fermion density in the plaquettes are able to suppress superconductivity.

Figure 9: Left to right: a) A resistance iso-line at  $R = 10^4 \Omega$  was found in the gate-gate map of device C2 b) The combination gate was swept at multiple temperatures. A clear separation between resistance lines in the two regimes is seen. The colorbar has <u>nothing</u> to do with the voltage of neither the top or frame gate but shows an arbitrary sweeping parameter.

#### 4.5 Magnetic Field Scan, Frustration

The final tuning parameter at our disposal is the magnetic field. Due to the plaquettes in the array we except periodic oscillatory behavior in the sheet resistance which is a unique feature for Josephson junctions array. In this section the response of the device to a magnetic field sweep is discussed. The behavior of each device was investigated in the puddle and junction regimes. The magnetic field is positioned perpendicular with respect to the plane of the array. No in-plane magnetic field was ever applied for any of the measurements.

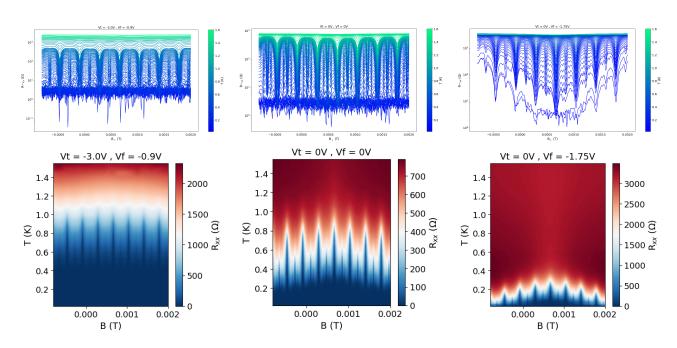

The data of the magnetic field sweep for device C2 and D3 are shown in the figures 11 and 10. The magnetic field and temperature dependence on the sheet resistance was measured at different positions in gate space. The experiment was conducted by sweeping the magnetic field at constant temperature. The same sweep was performed for multiple temperatures in the interval 20mK to 1,8K. This makes it possible to probe the stability of the ground state against thermal fluctuations. The most stable ground state is pushed out of superconductivity at higher temperatures than less stable ground states. The data is shown in 10. This presentation of the data allows one to see very small frustration features. Another presentation of the data is seen in 10. The sheet resistance is plotted as a function of temperature and magnetic field strength. This representation makes it very easy to see the effect of the two gate potentials on the magnetic field sweeps. Furthermore the BKT temperature is more easily identified. In this section the BKT temperature is referred to as the temperature at which the array becomes superconducting. This is not the exact definition since single vortices injected by the magnetic field might still have enough energy to overcome the pinning potential energy [21] I use the term BKT to indicate the temperature at which the array becomes resistive.

The behavior of the array for magnetic fields sweeps significantly depends on the position in gatespace. The sweeps were performed in all three regimes (junction, puddles and j+p regimes) and are showed in figure 10. The first picture a) shows the data for the device D3 in the junction regime i.e the top gate voltage is  $V_t = -3.0V$  and the frame gate voltage is  $V_f = -0.9V$ . As a function of the magnetic field, the sheet resistance is oscillatory which is the main characteristic feature of JJa's. It is difficult to identify the zeroth peak but it located at B = 0.66mT and the integer peak periodicity

Figure 10: From left to righta) The magnetic field scan of device D3 in the junction regime. b) The puddle+junction regime. c) The puddle regime.

#### is $375\mu B$ .

The most striking feature of the scan is the fact, that the data is perfectly periodic. The BKT temperature of all the integer peaks are the same at 1K. The half frustration peaks are observed between the integer peaks and their BKT temperature has been reduced to approximately 700mK. This clearly suggests that ground state at integer frustrations are more stable against thermal energy fluctuations compared to the ground state at half frustration. Very small dips in resistance can also be seen at frustration f = 1/3 are seen in figure 10. The sequence of most pronounced frustration peaks is therefore f = 0, f = 1/2 and f = 1/3.

Now the position in gate-space is changed to the J+P regime i.e. both the top gate and frame gate voltages are set to 0V. The data is shown in figure 10 b). Two remarkably features are seen. Firstly the BKT temperature of all frustration peaks have decreased. Secondly the magnitude of the decrease in BKT temperature is not the same for all frustration peaks i.e. the periodicity has become modulated. We are referring to this modulation as the envelope function. Frustration peaks at higher magnetic field strengths are more easily suppressed by thermal fluctuations. Surprisingly the 1/3 frustration peaks have become more pronounced in this regime.

Finally the the array is tuned to the puddles regime i.e. the top gate voltage remains at 0V and the frame gate voltage is set to  $V_f = -1.75V$  i.e. the junction conductance through the junctions are decreased by the electric potential. In this regime, the array barely becomes superconducting. This scenario is very similar to the measurement of the critical current in the puddle regime (figure 8). We suggest it is the same mechanism that is responsible for the suppression of superconductivity: Increasing the electron density in the puddles might cause an inverse proximity effect where the **amplitude** of the superconducting order parameter is suppressed. This effect seems to reduce the critical magnetic field of the superconducting gap. The peaks at f = 1/3 are still visible near the f =0 peak, but are significantly suppressed near frustration f = 2.

The three measurement in figure 10 support the idea of separating the physics of the array into different regimes in gate-space. The same trends are observed in device C2. A more systematic investigation of the top gate dependence was performed on device C2. The frame gate voltage was

Figure 11: A sequence of magnetic field scans of device C2 from the J+P regime to the junction regime. The top gate voltage was swept from 0.5V to -2.0V.

held constant at  $V_f = 0.2V$  while the top gate voltage was swept from 0.5V to -2.0V.

The sequence of magnetic field sweeps on device C2 is shown in figure 11. The top gate sweep can be visualized in the gate-gate figure 6 as a horizontal line from the J+P regime to the Junction regime.

The peak at B = -0.73mT is identified as the f = 0. The most visible and widest peaks are the integer frustrations. The periodicity of the integer peaks is  $430\mu B$ . The integer peaks are always visible and they are the most resilient against the temperature. Between the integers peaks, the f = 1/2 frustration peaks are seen. The superconducting ground state at half frustration is destroyed much earlier in temperature than the integer frustration. The half frustration peaks are flanked by two peaks which corresponds to f = 1/3 peaks. The f = 1/3 peaks are visible for most of the top gate values.

The general effect of the top gate voltage is clearly seen. Increasing the top gate voltage (in this context and in the rest of the thesis, the word "increasing" means changing the voltage to a more negative value), and thereby reducing the fermion density in the plaquettes, causes the envelope function on top of the frustration peaks to become less pronounced. At low top gates voltages, noninteger frustrations becomes suppressed at very low temperatures. Increasing the top gate voltage, the BKT temperature for all peaks are also increasing. The BKT temperature continues to increase until  $V_t = -2V$ , at which the frustration peaks are perfectly periodic (at least within the a range of six integer frustration peaks). At such high top gate voltages, the fermion density in the puddles is extremely low. Reducing the plaquette fermion density results in isolated superconducting islands and a more well-defined array. Intuitively, one would think that such a system should be well described by the XY model. The model Hamiltonian eq. 7 of the Josephson junction array suggests that all integer frustrations are identical. This certainly seems to be the case for device C2 in the junction regime, but not in the J+P regime. Due to the perfectly periodic frustration peak, the data suggests that the array is indeed well described by the XY model in the junction regime but more complicated physics must be included in puddle and j+P regimes. In order to explain the envelope function, [34] suggests that the coupling constant (The Josephson energy) in the hamiltonian (equation 7) no longer

Figure 12: The ground state configuration of vortex lattice at rational frustrations. [34]

is constant, but is dependent on both the temperature and the magnetic field.

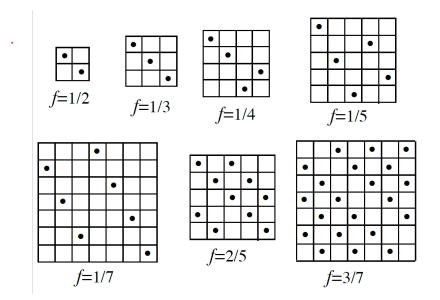

The features seen in the magnetic field scans can be explained by considering the dynamics of the vortices in the array. Vortices move in the periodic pinning potential generated by the underlying Josephson lattice [31]. The stability of the vortex lattice is determined by a competition between vortex-vortex interactions (which is determined by the mean distance between vortices) and commensurability with the underlying vortex pinning potential from the Josephson junction array [36]. At rational values of the frustration f = p/q, the vortex lattice induced by the magnetic field is commensurate with the Josephson junction array and the vortex lattice forms a superlattice of size q time q [19]. The vortex lattice at rational frustration can be visualized as regular lattice shown in figure 12. The hamiltonian of the XY model can be mapped into a Coulomb gas with "charge"  $n_i + f$  where  $n_i$  is the vortex vorticity [34].

The relative stability of the vortex lattice at rational frustration depends on the coordination number of the array. For square arrays, the sequence of frustrations beginning with the most stable lattice is f=1/2, f=1/3, f=1/4, f=2/5, which have both been simulated and observed experimentally [20]. It is clear from our data, that we see the same sequence of relative stability in both devices. Experimentally the stability of the peaks are determined by their BKT temperature. The dips in the resistance occurs due to formation a stationary vortex lattice and its stability is inferred by the temperature at which the lattice is broken and the array becomes resistive. Interestingly, the frustration peaks at f =1/4 and smaller values cannot be seen in any of our measurements.

The general effect of the magnetic field on the array resistance have been introduced. The effects of all the available tuning parameters have been accounted for.

#### 4.6 Precise determination of frustration

The main focus of this project is to study the SIT quantum phase transition the array as a function of frustration. More specifically we have investigated the zero bias resistance as a function of temperature at a handful of precisely selected values of frustration: 0, 1, 1/2 and an irrationals. The first irrational value is approximated as f = 0.22 and the second irrational value is chosen to be  $f = (3 - \sqrt{5})/2$ .

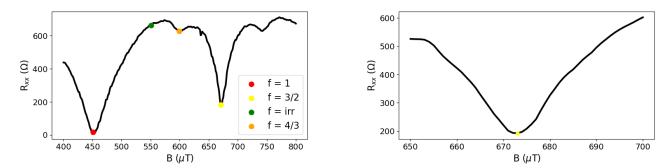

Therefore it is important that the tuning of the magnetic field is accurate. Theoretically it is possible to determine the precise value of the magnetic field since the area of the plaquettes are known. But this is experimental physics, so everything is always harder than it sounds. We observed that the value would slightly change for each measurement. Both the precise position and the period between frustration peaks slightly fluctuates between each experiment. Therefore we used the following method to determine the frustration parameter as precisely as possible before each measurement: Firstly the gate space parameters are chosen. Secondly a resistance vs magnetic field scan is started. Such as scan is shown in figure 13. The majority of these magnetic field scans were done at higher temperatures than base 15 mK since the frustration effects often aren't visible in the superconducting state. The array was made slightly resistive either by increasing the temperature (up to 400 mK) or by applying a small DC bias current. The data in figure 13 shows a scan for device C2 in the junction regime at 400mK. The lockin time integration constant was usually set to a low value for the large scan.

Figure 13: From left to right. a) The magnetic field scan is used to determine the precise value of the frustration parameter. We identify f = 1 as the first large dip in resistance. b) A small scan with higher lockin integration time was performed in the vicinity of the desired frustration.

In the large scan, the following frustrations are seen: f = 1 at  $451\mu$ T, f = 3/2 at  $671\mu$ T, f = 4/3 at  $148\mu$ T and f = 0.22 at  $551 \mu$ T. A more refined scan was started after the wide magnetic field scan. The magnetic field value was centered around the desired frustration value and the lockin integration time was increased. Usually it was set to 3 seconds.

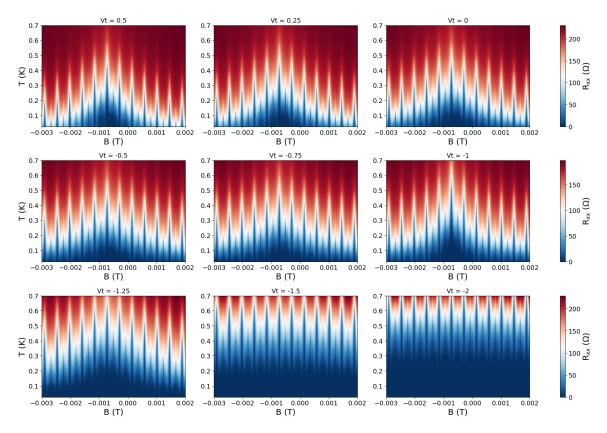

#### 4.7 The superconductor to insulator transition

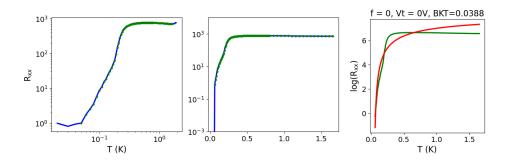

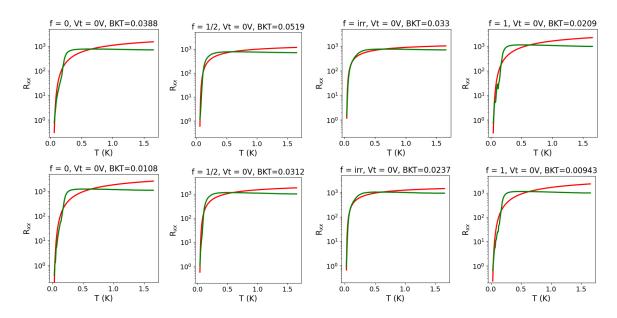

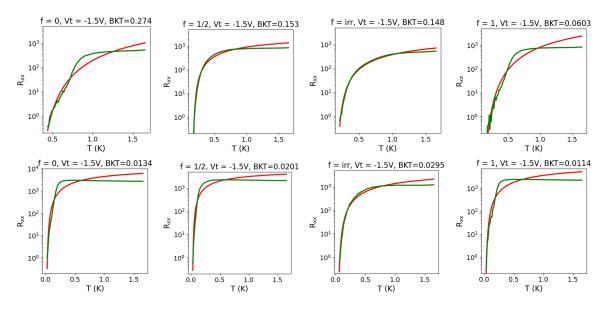

This section introduces the main results of the thesis namely the investigation of the SIT quantum phase transition. During the experiments, we quickly discovered that the SIT significantly depended on the top gate voltage and the frustration. The main features we investigated have been the BKT transition and the low temperature resistance saturation.

In this section, a phenomenological description is presented of the BKT transition in Josephson junction arrays and the appearance of resistance saturation at low temperatures. The first of our main research questions has been under what circumstances the resistance saturation occurs. Specifically we have been investigating how the prevalence of the anomalous metallic phase changes between the junction and puddle regimes. Furthermore, the prevalence of the resistance saturation as a function frustration was investigated in both regimes.

Our second research questions has been in what regimes and at which frustrations the resistance lines deviate from the "perfect" BKT transition. We have been investigating how the resistance lines deviates from the ideal BKT transition line by analyzing the curvature of the resistance lines and by fitting our data to the predicted BKT line. In this section our data of the SIT's are presented.

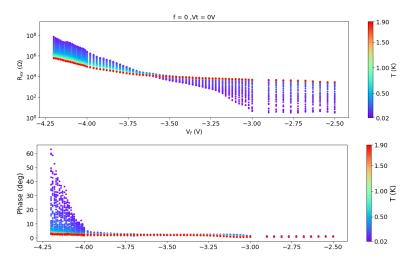

A typical measurement of device C2 is shown in figure 14. The frame gate was swept from -2.5V to -4.2V while the temperature was kept constant. The frame gate sweep was done for 100 temperatures in the range 0.02 to 1.9 K. The temperature interval is 20mK to 800mK in 10mK increments, and from 850mK to 1.9K in 50mK increment. Similar frame gate sweep measurement was done at top gate voltages 0V, -1.5V, -2.0V and -4.0V and at frustration f=0, 1, 1/2 and irrational. The top picture shows the sheet resistance as a function of the frame gate voltage at multiple temperatures. The lockin phase of the preamplified current was also recorded for each scan and is shown in the bottom picture. It is seen that the lockin phase remains below 20 degrees for the majority of the scan but at  $V_f = -4.0V$  the phase drastically increases to approximately 90 degrees. A large shift is caused by

Figure 14: The top figure shows the data of a typical measurement. The resistance is calculated by dividing the voltage drop across the sample device by the current (and divided by the voltage and current preamplifier constants). The bottom figure shows the phase of the preamplified current. When the array becomes insulating, the phase of the current significantly increases.

inductive or capacitive circuit elements. Since no such elements should be present, we exclude data in the analysis if the lockin phase reaches large values. The threshold value for device C2 was set to 20 degrees and for device it is 30 degrees. The large phase shift occurs when the array becomes highly resistive. We suspect this has something to do with the current preamplifier (The Basel). The IV-converter has an internal resistance proportional to the gain. When the array becomes insulating, the sample resistance and the internal resistance of the IV-converter become comparable.

In order to circumvent this problem, the gain on the preamplifier could be further increased. This however would overload the lockin amplifier. The preamplifier gain was  $10^8$  for all the measurements.

A vertical line cut at a constant frame gate voltage indicates the current phase of the system. At Vf = -2.5V the array resistance is decreasing when the temperature is going towards zero which is characteristic of the superconducting phase. The opposite occurs at Vf = -4.0V where the resistance is increasing when the temperature is going towards zero. This is the main characteristic of the insulating phase. The line at which the temperature dependence of the resistance switches is referred to as a separatrix between the superconductive and insulating phases. Plotting the vertical line cuts in figure 14 generally is how researches present their SIT measurements i.e the resistance lines as a function of temperature.

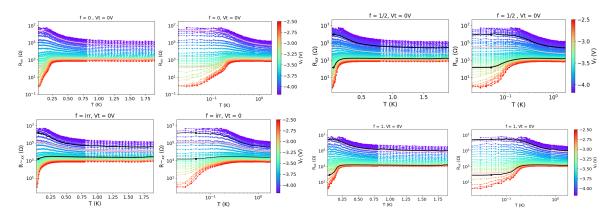

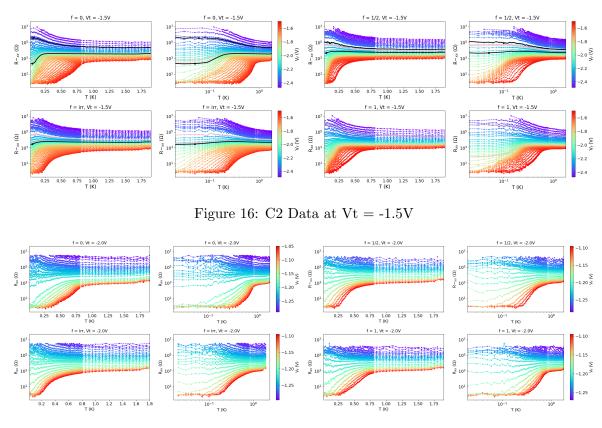

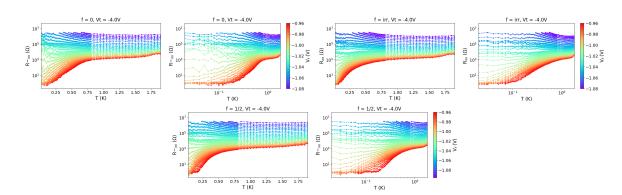

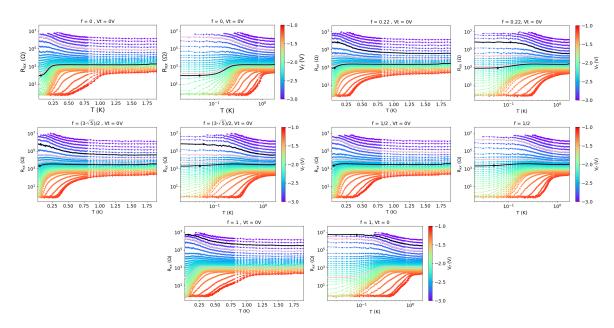

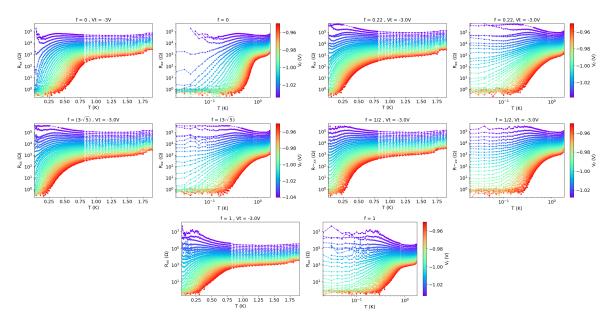

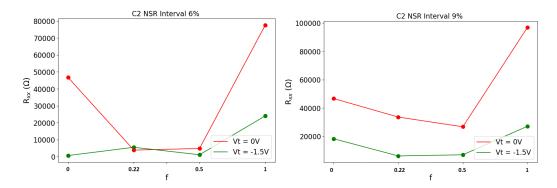

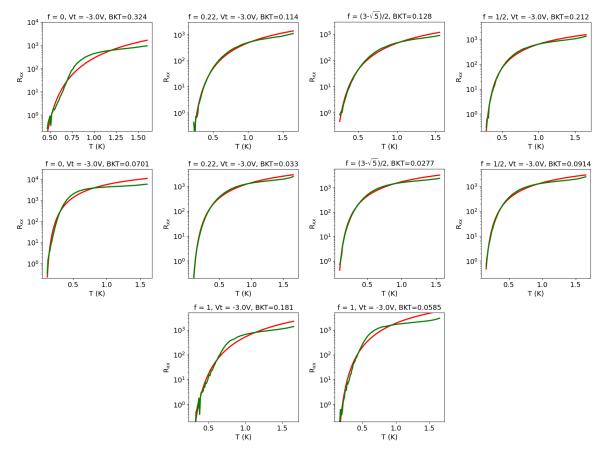

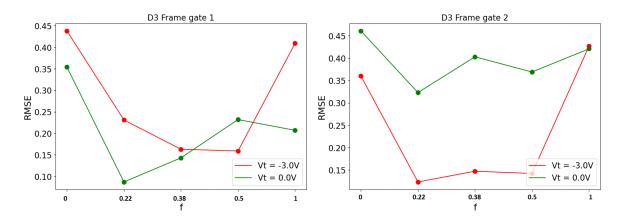

The entire data set of the SIT experiments are shown in following figures. This may be slightly overwhelming for the reader, but it allows to more easily see the effects of the frustration and top gate voltage. The SIT's of device C2 are shown in figure 15 to 18 and of device D3 in figure 19 to 20. The pink and black lines are used in the analysis in the following section, and will be explained. The data in these figures have been normalized with respect to the aspect ratio of the array aspect ratio (3.77) hence the maximal resistance that can be trusted is approximately  $10M\Omega$ . The figures are grouped based on the top gate voltage. The ranges/interval of the frame gate is not the same for measurements at different top gates since the frame gate interval required to push the array out of superconductivity is simply not the same in the different regimes.

#### 4.7.1 Device C2

The top gate and frustration parameters are independently tuned, so ideally each of their effect on the SIT . It turns out to be more complicated since each tuning variable maybe cause the same changes in the SIT data. Furthermore it is difficult to directly compare the measurements of device C2 at

different top gate voltage since the frame gate interval used to drive the SIT is not the same. The frustration dependence on the SIT at fixed top gate voltage is more easily compared. It is seen that frustration causes the SITs to change in multiple ways. When the frustration is set to irrational of half frustration, the BKT temperate decreases. The BKT temperature at f = 1 often is slightly smaller than at f = 0. This trend has already been observed in the magnetic field scan in figure 11.

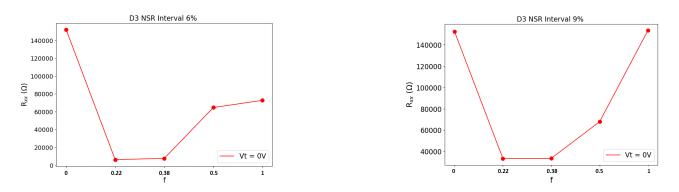

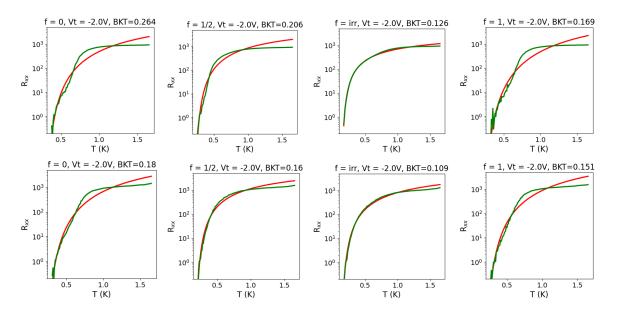

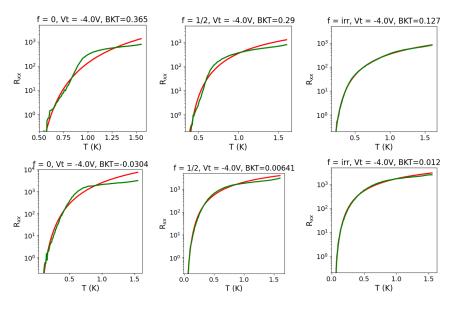

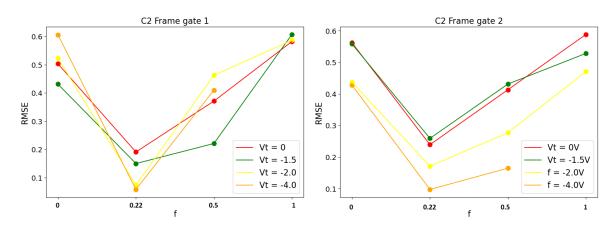

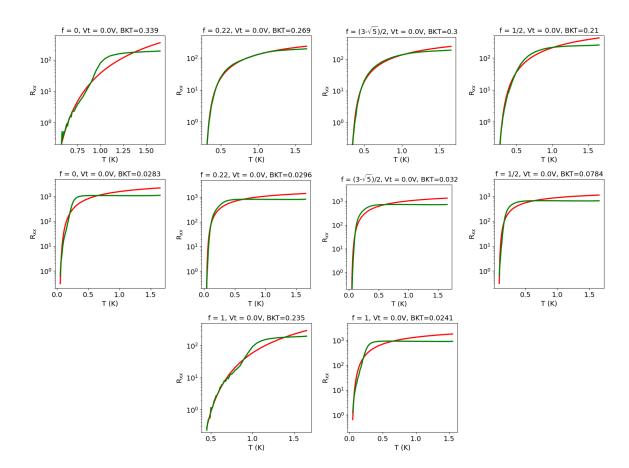

When the frustration is changed, it causes the curvature of the resistance lines to change. This is very clearly seen in figure 25. Qualitatively the is a difference between the curvature of the superconducting lines at f = 0 and f = 0.22. This feature is very surprising and will be discussed in details in later sections. Finally it is seen that the prevalence of low-temperature